Other Parts Discussed in Thread: AM623, AM6546, AM6442, AM2432, TDA4VH-Q1, TDA4VH

Tool/software:

HI TI experts,

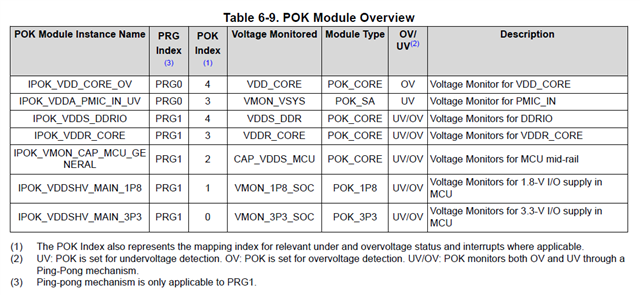

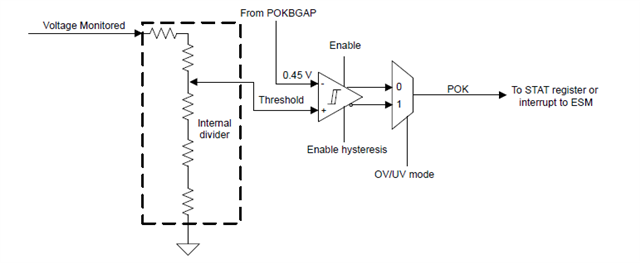

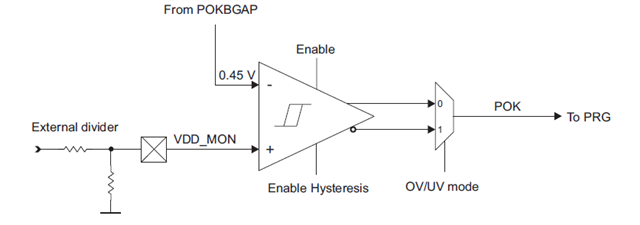

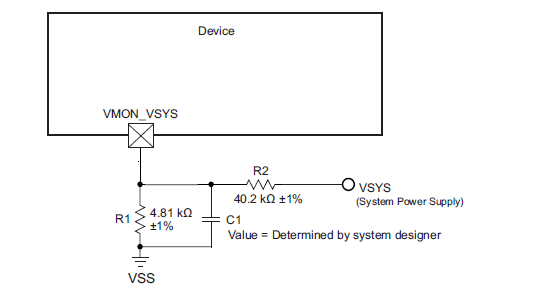

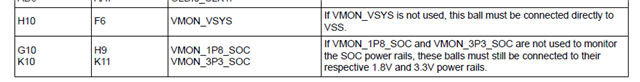

I have queries related to the voltage monitoring capability of the SOC POK module types, accuracy., design recommendations and supported rails.