Other Parts Discussed in Thread: TMDS64EVM, CDCI6214

Tool/software:

Hi

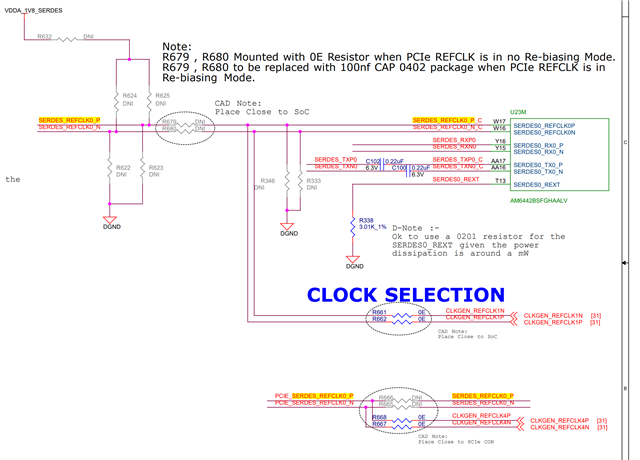

I found in AM64 evm schematic, there is a description about PCIE clk.

I want to know what is meaning of re-biasing mode?

Regards

Zekun

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

And what is the minimum current for powering EVM?

User guide shows that the maximum is 12V 5A, but what is the minimum limit? EVM is TMDS64EVM.

Regards

Zekun

Hi

Any updates here?

Hello Zekun

I added my input based on my understanding. I would expect dave to add additional thoughts.

I found in AM64 evm schematic, there is a description about PCIE clk.

I want to know what is meaning of re-biasing mode?

Currently the SOC and the external connector is being clocked by CDCI6214RGET

Alternatively PCIe clock from the SOC could be configured as the REFCLK or External clock can connected to the SOC

When the clocks are compatible HCSL the below is the recommended changes

R679 , R680 Mounted with 0E Resistor when PCIe REFCLK is in no Re-biasing Mode.

R665, R666 mounted

R667, R668 DNI

When the clocks are not compatible HCSL - LVDS ( interface an LVDS output with an HSCL-compliant input) the below is the recommended changes

R679 , R680 to be replaced with 100nf CAP 0402 package when PCIe REFCLK is in

Re-biasing Mode.

R665, R666 mounted

R667, R668 DNI

Regards,

Sreenivasa

Hello Zekun

And what is the minimum current for powering EVM?

User guide shows that the maximum is 12V 5A, but what is the minimum limit? EVM is TMDS64EVM.

It is recommended to add a new E2E for the power question and not mix with the PCIe query.

This helps in follow-up as well as reuse.

Regards,

Sreenivasa

Just to add to Sreenivasa's comment:

The EVM was designed to support multiple SERDES clocking configurations, hence the need for different BOM stuff options.

SERDES0 REFCLKP/N requires HCSL-level inputs when operating in input mode.

In the default (shipped) state, PCIe REFCLK is supplied to both the SoC and the PCIe connector via the CDCI6214 clock generator device operating in HCSL mode. For TMDS64GPEVM Revision PROC101B(001) you will find the required on-board 49.9 (1%) Ohm termination resistors for same installed as R681/R682 and R683/R684 respectively.

Thanks, Team.

Close it.

Regards

Zekun