Tool/software:

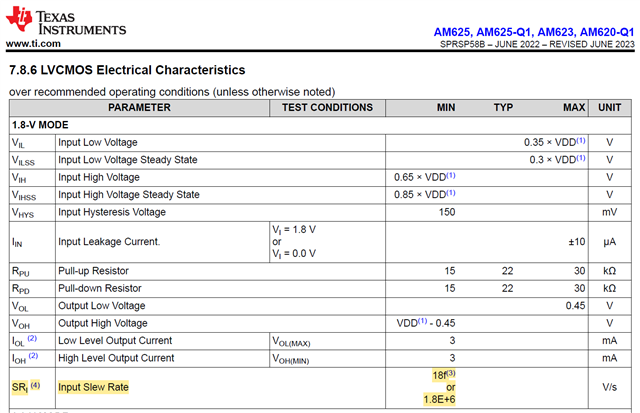

#1. Did not find MMC0 HS200 slew rate data in datasheet timing section, so section 7.8.6 LVCMOS Electrical Characteristics data applies?

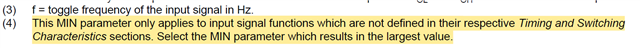

#2. The Min vale: 18f or 1.8E+6, the two value are quite different, 18f=18x200MHz, 1.8E+6=1.8M for HS200, which is the right one for HS200?

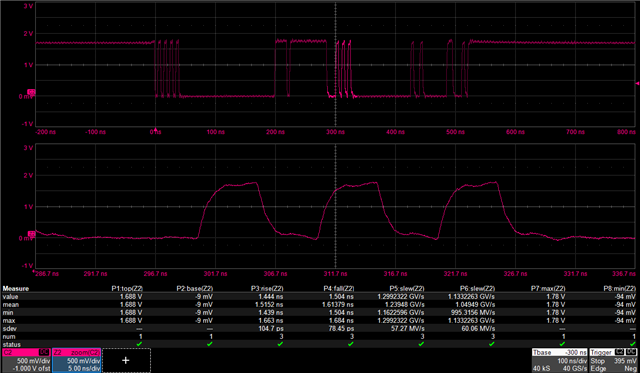

#3. On custom board, the slew rate of read data with eMMC is about 1V/ns, see below picture, P5 and P6 for rising and falling edge slew rate, Is it acceptable for AM62x at HS200?

#4. How is the slew rate requirements specified? What impaction if lower slew rate signal?