Hi,

I would like to ask a question on OMAPL138 DDR2 routing.

|

|

OMAP L138 |

DM643x |

|

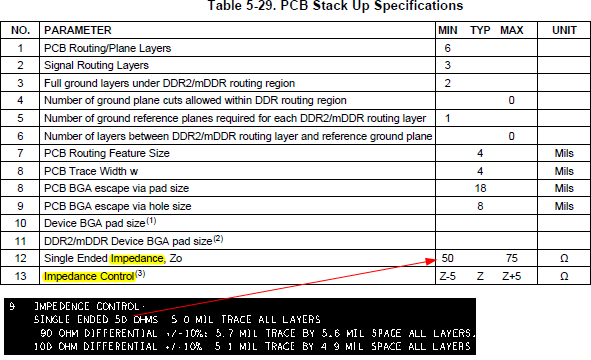

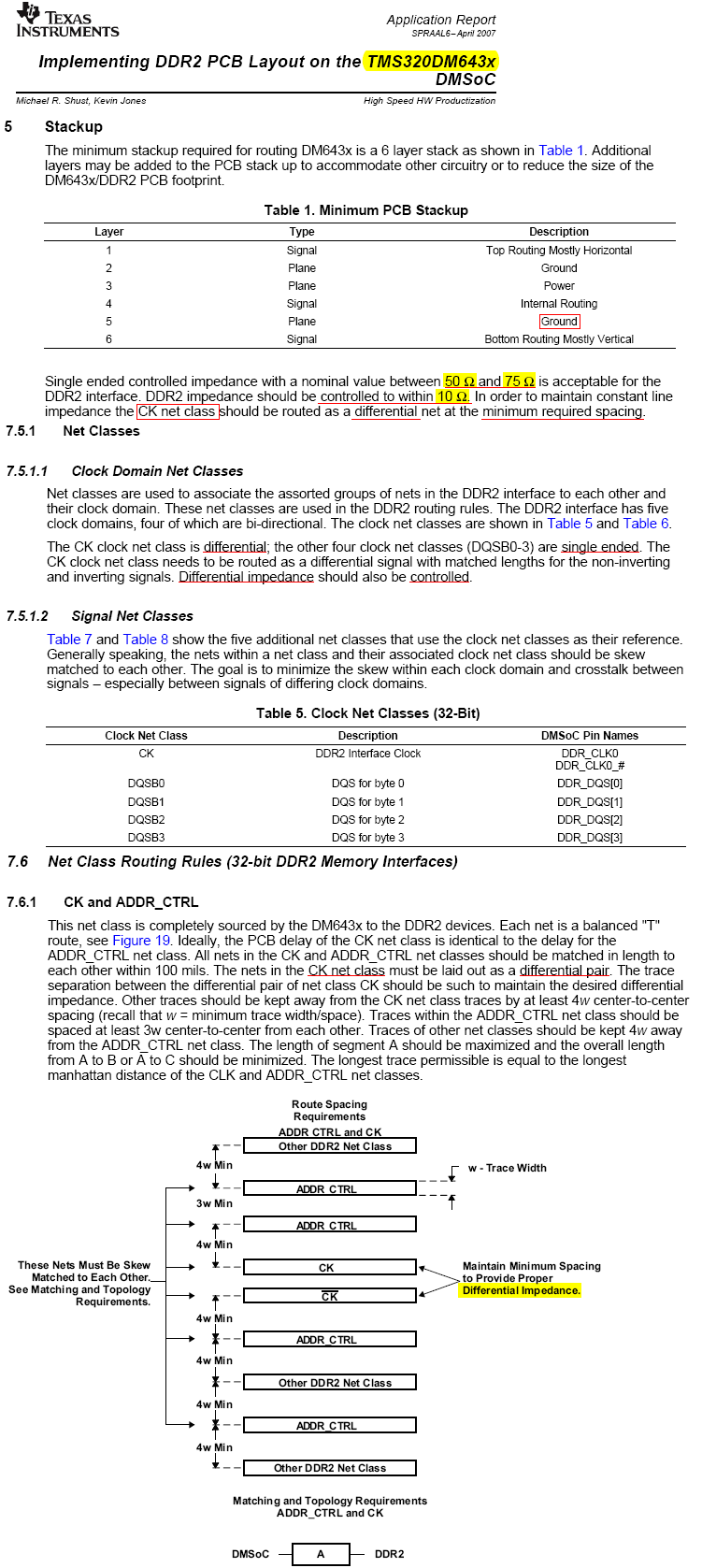

(1) Implementing DDR2 PCB Layout on the TMS320DM643x DMSoC, SPRAAL6 |

|

✓ |

|

(2) Understanding TI's PCB Routing Rule-Based DDR Timing Specification, SPRAAV0A |

✓ |

✓ |

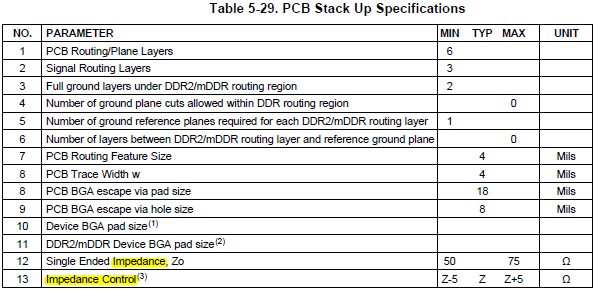

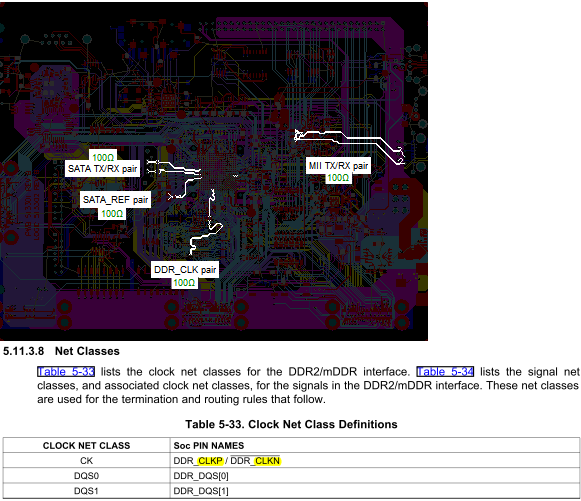

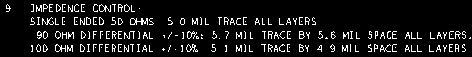

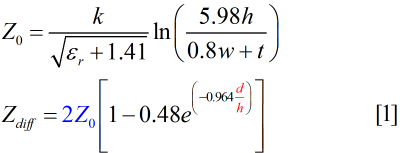

(1) contains lots of exact specifications such as wire impedance, net class, differential class, differential impedance and so on, many down to prescribed values; In contrast, (2) reads like a gentle introduction to novice users.

However, without figures as in (1), there is no way to determine whether the routed board matches basic DDR2 timing and routing constraints. So does a counterpart of (1) for OMAP L138 exist?

Zheng