Part Number: AUDIO-AM275-EVM

Other Parts Discussed in Thread: UNIFLASH, FFTLIB

Hello Team,

I am trying to build a custom AWE application to run on C7x cores of the AM275 EVM and was going through the SDK to find an appropriate place to integrate a custom AWE module - in my case DiracAwe module. Based on my experience with custom AWE modules, there are 2 files in the AM275-AWE-SDK_11.01.16.06 SDK that need mandatory updates:

packages\dspc\c7x\am275x\AWECore\Include\ModuleList.h

packages\dspc\c7x\am275x\AWECore\Designs\passthrough_InitAWB.c

Can you please confirm this?

When I build the SDK for say c75_0 core, I see the below files built:

.

-- audioApp_c7x_0.release.appimage

-- audioApp_c7x_0.release.appimage.hs_fs

-- audioApp_c7x_0.release.appimage_xip

-- audioApp_c7x_0.release.map

-- audioApp_c7x_0.release.out

According to the Audio SDK User's Guide, it mentions for the above use case, (Config1) I need:

SD Card setup

tiboot3.bin: This is SD secondary bootloaderapp_r50_0: This binary gets loaded on R5F0_0, and it works as tuning gatewayapp_dsp0_0: This code runs on C75_0 dsp, it runs audio signal-chain and AWEcore

I would like to understand:

- the role of the generated files above (especially .out, .appimage, .appimage.hs_fs). Do they need to be copied to the SD card? Or is it copied via some utility like uart_uniflash.py?

- what are the absolute dependencies to build the application binary for linking? Would linking my custom library by including it's path in audio_app\am275\asdk_am275_includes.mak be suffcient? I do understand freertos*.lib is necessary. I would also require audio peripherals (MCASP) and UART related libraries as well. But won't be needing to link FFTLIB and DSPLIB since those are selectively included in my static library for DiracAwe.

Please do advise. Looking forward to hearing from you,

Regards,

Sreekanth

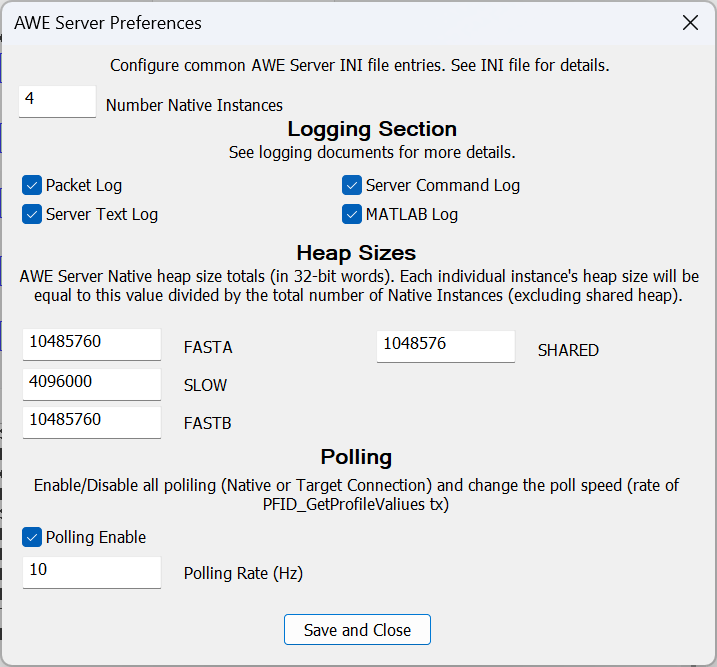

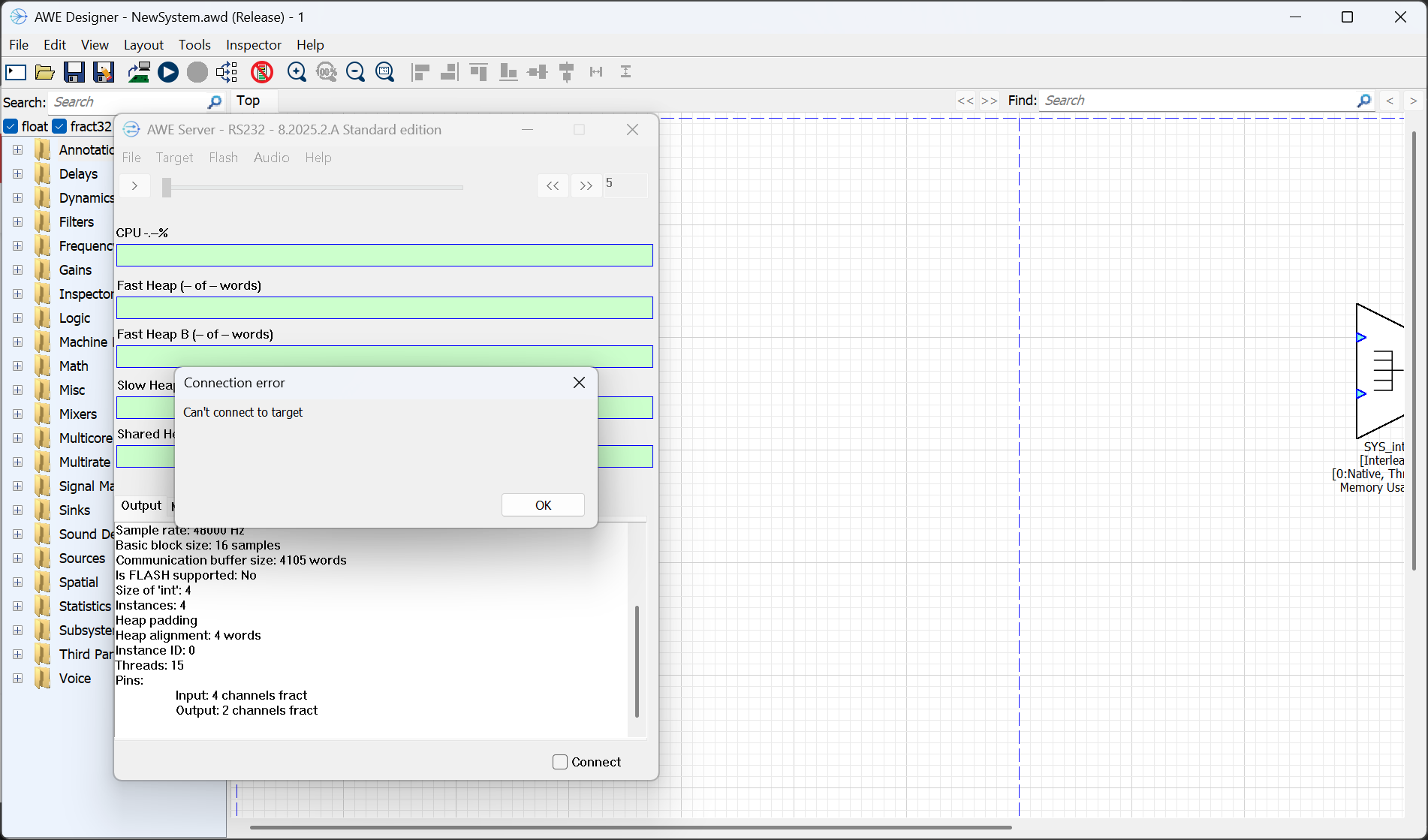

I could only enable AWE Server logging as:

I could only enable AWE Server logging as: