I would like to run the three cores of the C6474 simultaneously and detect the completion somehow. Is there any method to do that without DSP/BIOS?

Another silly question, why we use DSP/BIOS? what is the uniqueness and advantages of using DSP/BIOS?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

I would like to run the three cores of the C6474 simultaneously and detect the completion somehow. Is there any method to do that without DSP/BIOS?

Another silly question, why we use DSP/BIOS? what is the uniqueness and advantages of using DSP/BIOS?

beaver said:I would like to run the three cores of the C6474 simultaneously and detect the completion somehow. Is there any method to do that without DSP/BIOS?

I need you to explain more about what you want to understand here. "run ... simultaneously" can be interpreted many ways, and the same is true for "detect the completion".

The easiest answer is that the Parallel Debug Manager (PDM) and CCS take care of it all for you. When you open CCS on a C6474, the PDM opens and you can open a CCS window for all three cores. After loading your programs into each core in their respective windows, you can set breakpoints at the end of the applications. In PDM, you can select the three cores and start them running simultaneously, and when they finish they will all show "Halted" in the PDM window.

That is probably not what you want, so help me understand more about your question.

beaver said:Another silly question, why we use DSP/BIOS? what is the uniqueness and advantages of using DSP/BIOS?

DSP/BIOS is a real-time kernel. It includes real-time analysis tools to help you in debug. It gives you a simple way to implement things that you might need in your system, like periodic interrupts, separated tasks, and communication channels.

You can look through the training material starting from www.ti.com to find some good background on DSP/BIOS.

To almost quote from one of our Technical Training Organization's Student Guides:

"Every system has an operating system – whether it is a while-loop in main() with some flag variables you set in the ISRs, or something specialized purchased from a 3rd party, or Linux. In every system, you have to do basic system configuration and initialization while allowing you to implement your data processing and I/O coupled with events and ISR.

"DSP/BIOS is TI's O/S for real-time applications. DSP/BIOS has been around for many years and is in tens of thousands of systems. That is a lot of experience for a specialized operating system. Plus, through all of these designs, we continue to verify functionality and ensure success.

"Every O/S requires overhead – one way or the other. So, when you research the memory and code utilization, we are talking about 1-4% overhead over your entire system – very little if you ask most engineers. Also, you cannot compare this to 0%, because every system requires overhead for an O/S – homegrown or not. On top of that, the APIs are already written for you. In most cases, you have a simple API call and an object (via the GUI) to fill in. It is simple to use and the total cost for DSP/BIOS is ZERO – it comes standard with any CCS installation."

I personalized that quotation a little bit. I did not use all of it. But I did not have to write it all myself since someone else had already done it for me. That is what DSP/BIOS brings to you - many common features are already implemented so you can just think about your application and not how to collect statistics or signal between tasks.

Thank you for your reply.

"run ... simultaneously" here I mean is configuring one core as the master core, the other two will be the slave cores. Then the master core can trigger all the three cores to run simultaneously (by sending some sort of notification). Then once the processing on each core is completed, the master core will know.

My question is: Without DSP/BIOS, can we do that?

Do you want to do this just on the bench through CCS? Or standalone after booting from some boot mode? If standalone from a boot mode, which boot mode will you use?

What kind of notification would you like?

I am confident that I will answer your question or point you to the right place to find the answer, but I still want to narrow the universe of answers down a little.

beaver said:My question is: Without DSP/BIOS, can we do that?

The answer is "yes". But I am curious why you think that DSP/BIOS helps with running multiple cores at the same time and signalling completion of tasks. As far as I can tell, there are no tools or hooks in DSP/BIOS to specifically support this. I have not played with BIOS 6, yet, so if that is where the real answers are, please let me know. Or if you have some specific DSP/BIOS ideas for it, please let me know.

One suggestion - use the inter-DSP interrupt registers (IPCGR0-2 and IPCAR0-2). Check out section 3.5 in teh datasheet. Core 0 can write to the registers for cores 1 and 2. When cores 1 and 2 respoind to the interrupt either through and ISR or by polling they can execute the desired code. When cores 1 and 2 have completed their execution they can in turn write to the register for core 0 as notificaiton of completion. Other methods could also be used.

Thank you again for your reply. I have no preference on the bench through CCS or boot mode and no preference on the notification. Any notification which can let the master core know the completion of slave cores will work for me.

I am interested in another features, which I don't know how to implement. How to pass the buffer address from the slave cores to the master cores?

Is there any example code for this method?

Attached is example / demo code for running sequential processing on all three cores of the C6474. This version uses DSP//BIOS constructs, like tasks and semaphores. It also uses EDMA to transfer data from the one core's L2 SRAM to the next core's L2 SRAM and implements interrupts after the transfers complete (to the initiating core). And it uses the Inter-Processor Communication (IPC) registers to generate signalling interrupts on the next core.

In the comments at the top of main.c, you will find an explanation of what is happening in the demo code and instructions on how to run it so you can see the behavior of the data movement and processing.

In this code, I use the simplest method I know of to run demos on 3 cores. All of the cores run identical code, which is duplicated when loaded into their own local L2 SRAMs. Using the Chip-Level register to determine the CoreNumber, each core can then run with slightly different run-time variables. This is just one of the ways you can run code on multiple cores; I find it very easy to do with just a little worry about synchronizing and timing. For more good ideas on writing code for multiple cores, see the Multicore Programming Guide.

For your latest quesiton about sending information between two cores, there are a couple of options. I tend to go with the low-level approach of defining a shared memory location that will have information needed for a target routine, have the sourcing core fill the parameters in that shared memory location (usually a struct), and then signal the target core using an IPC interrupt call.

The higher-level approach is to use the DSP/BIOS MSGQ system by using the Shared Memory messaging transport mechanism. You can download this package, which includes an app note explaining how to use it, from the Update Advisor site, http://software-dl.ti.com/dsps/dsps_registered_sw/sdo_sb/targetcontent/MQT/index.html .

Vyom,

Here is the link to the IPC software product.

http://software-dl.ti.com/dsps/dsps_public_sw/sdo_sb/targetcontent/ipc/index.html

The BIOS IPC Product contains modules that support the communication between processors in a multi-processor environment and communication to peripherals. This communication includes message passing, streams, and linked lists. These modules work transparently in both uni-processor and multi-processor configurations. I think the IPC package also supports the 647x platform. Please download the package and go through the documentation and sample applications.

Regards,

Nag

(If your question is answered, please click the Verify Answer button on this post)

Hello RandyP,

Please i want to execute one code in 3 cores of C6474 ( parallelising code ) ,

My question is there is no other way to do that without using DSP/BIOS ?

If this no possible please tell me the way to execute the example C6474_Edma_IPC_BIOS in CCS V5 .

Thank you in advance

smeil,

Please look at another thread, specifically TMDSEVM6474L EDMA interrupt example problem, where I posted a non-BIOS version of this same project. Both were written for and tested in CCS 3.3 and have not been migrated to CCSv4 or CCSv5, at least not by me.

In the referenced thread, I noticed that I made a short comment about running it in CCSv4, and it should be just as easy to do this in CCSv5.

If you decide to try it in CCSv5, please try the following steps to import the project:

Please let me know how this procedure works, if you try it. And whether you use CCS 3.3 or CCSv5, please let me know if you are able to get the example to run the way you want it to work.

Regards,

RandyP

If you need more help, please reply back. If this answers the question, please click Verify Answer , below.

Hello Randyp

Thank you for your help ,

I followed the steps to import project like you mentionned above..

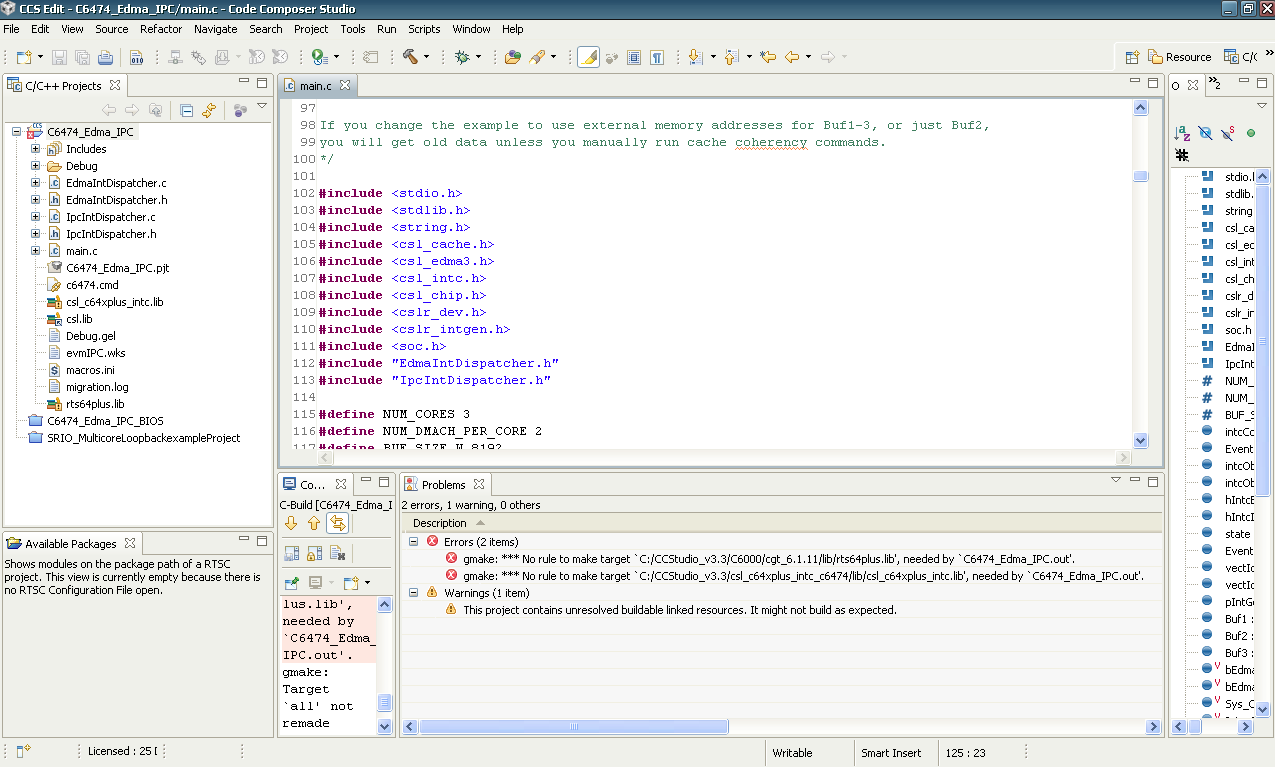

but after building project the Errors appears in console (view attached image screen )

other remark is i don't have the folder csl_c64xplus_intc_c6474 ?

I have just the two folder below

C:\CCStudio_v3.3\boards\evmc6474_v1\csl_c64xplus_intc

C:\CCStudio_v3.3\boards\evmc6474_v1\csl_C6474

so the you have any idea to resolve this problem ?

smeil smaili,

Thank you for the feedback. I am not sure what the "correct" way to make these projects more portable is, but I have seen a Wiki topic that talks about it. It would have helped you if I had implemented better procedures. Your feedback will help me do a better job in the future.

smeil smaili said:i don't have the folder csl_c64xplus_intc_c6474 ?

I have just the two folder below

C:\CCStudio_v3.3\boards\evmc6474_v1\csl_c64xplus_intc

C:\CCStudio_v3.3\boards\evmc6474_v1\csl_C6474

In my CCStudio_v3.3 folder, I have several csl_Cxxxx folders and have a matching csl_c64plus_intc_cxxxx folder. They may be identical, but to be safe I tend to keep copies of each one that is unique to the device. With CCSv4/v5, I tend to also have a unique workspace folder for each device or EVM and keep the CSL folders inside that workspace so they are easy to reach from any project in that folder. Like you, I just link to the CCS 3.3 version for these cases where I have imported from CCS 3.3. And this causes the issues that you have, because you are importing my CCS 3.3 project.

I think that the easiest solution to your two errors are:

My personal choice for a case like this is to delete all three of the *.lib files from the project list. I am not used to seeing libraries in there, and I prefer to include them in the Build Properties. Using environment variables would make it much more portable, or copying the CSL folders into the CCSv4/v5 workspace so they are workspace- and project-relative would work, too. Then you have to make the same changes in C/C++ Build->Settings: under the Tools Settings tab and the C6000 Linker, click on File Search Path and manually add "csl.lib" and "csl_c64plus_intc.lib" in the Include library file box and manually add the two paths to your CSL folders in the Add <dir> to library search path box. You may want to delete the ${C6000_CSL_CG_ROOT}/lib line if it is in there.

If either of these get your project to build successfully, that will be great. Please let me know what method you used and what your opinion is about the process. I almost always do the manual steps, partly so I know exactly where things are coming from when I do my build. But your opinion may be very different, and I would appreciate to read your opinion about this process.

Regards,

RandyP

Hello RandyP,

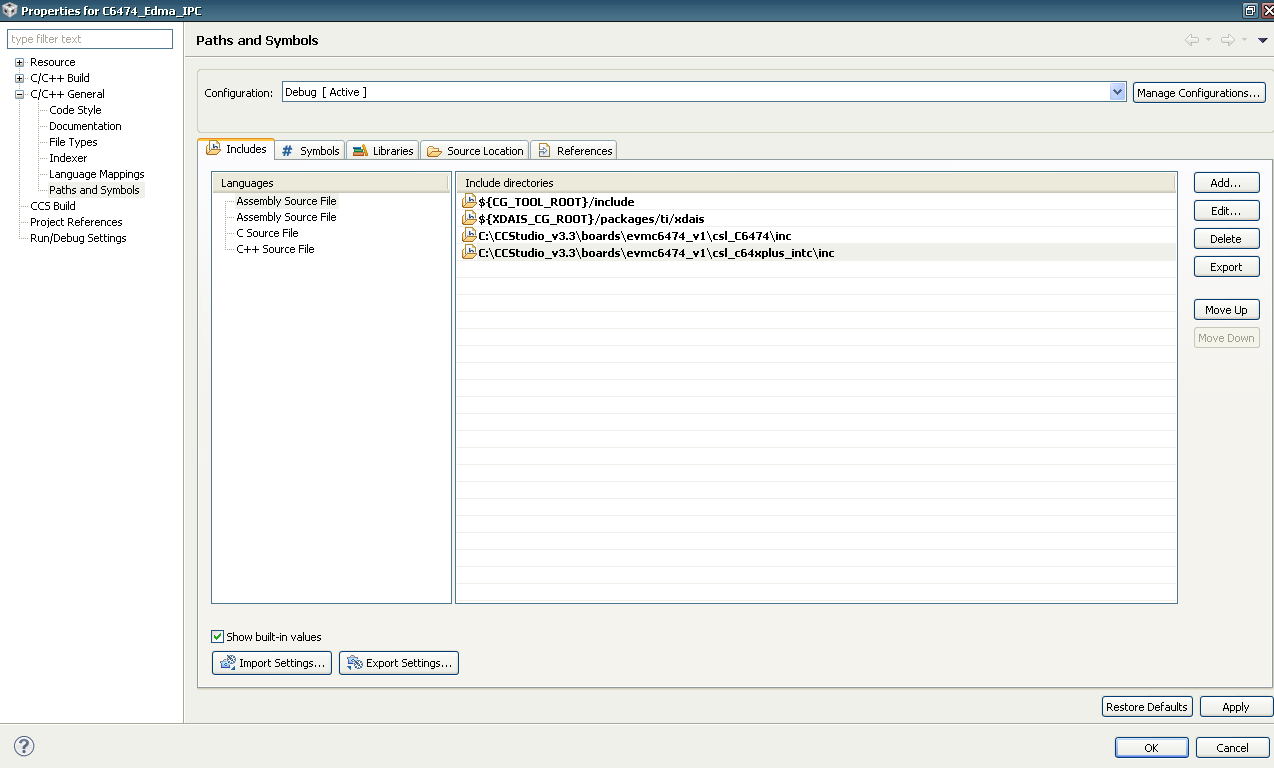

for final modifications who i made are :

in paths and Symbols :

C:\CCStudio_v3.3\boards\evmc6474_v1\csl_c64xplus_intc\inc

C:\CCStudio_v3.3\boards\evmc6474_v1\csl_C6474\inc

${XDAIS_CG_ROOT}/packages/ti/xdais

${CG_TOOL_ROOT}/include

in the C6474_Edma_IPC.pjt

i deleted the line Source="..\..\C6000\cgt_6.1.11\lib\rts64plus.lib"

After that i build the project successfully without any Errors or Warnings .

But ,In the steps mentionned in main.c file to execute the example ... After i loaded the program in three core ...i don't found in the Menu Bar

GEL->Debug .....

So, i can't show the 3 buffers after executing program !

All the GEL Debug did was to open three Memory Windows for the three buffers. I do not know how to do that in CCSv4, but you can easily do it manually. Just open a Memory Window and tell it the name of the first buffer, then click New Memory Window, twice, and supply the names of the second and third buffers. You will need to enter these buffer names with each of the cores selected, separately.

Regards,

RandyP

If you need more help, please reply back. If this answers the question, please click Verify Answer , below.