Hi,

I have a question about DDR3 Write leveling process :

During write leveling, DSP(6678) is shifting its DQS output relative to CLK output while monitoring ALL the DQ inputs. Normally the DDR3 should drive out its prime DQ depending on DQS/CLK while maintaining other DQ outputs to "0".

What happens when, due to PCB dammage, one of the DSP DQ (other than prime DQ) is externally unconnected, therefore not driven (being Hi-Z) during the write leveling process ?

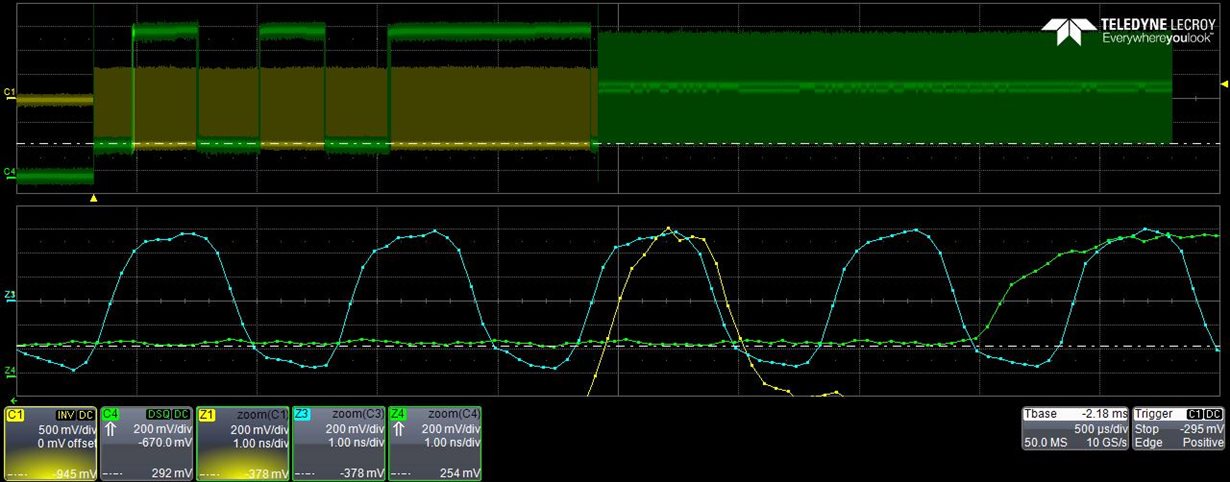

The next observation has been taken in a system where DDR-DQ12 connection to DSP is broken, all other connections remaining OK. The scope picture shows signals taken at the DDR3 balls, DDR-prime-DQ8(green) / DQS(yellow) / CLK(blue), starting from the write leveling process.

One can see that although the DDR-DQ8 changes to '1' once the adequate DQS position relative to CLK has been achieved, the process does not stop. DQS continues being shifted again and again during a lot of time (more than 1 ms) before switching to read leveling. Several complete CLK periods are covered, therefore causing the DDR prime DQ to switch back to "0", and so on...

Do you confirm that even if not prime DQ, one DSP DQ input remaining undriven during write leveling could cause the leveling process to fail (for example because of false triggering due to Hi-Z input) ?

Or are there some other reasons that could cause the write levelling to act this way ?

With best regards,

Bruno