Hi,

I am currently aiming for SRIO PRBS testing in a configuration where the 66AK2H14 will receive PRBS23 pattern from external driver.

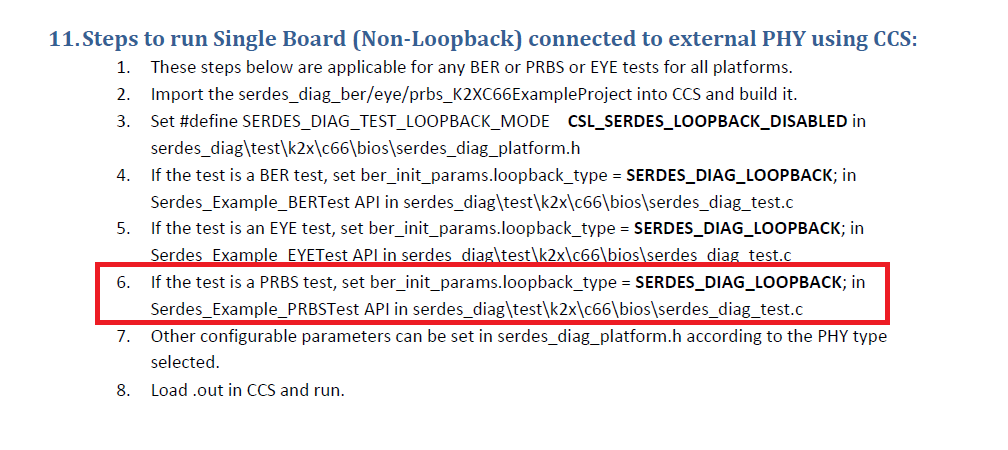

I read the "serdes_diag_user_guide " (June 2017) document and prepared the required modification :

I first set SERDES_DIAG_TEST_LOOPBACK_MODE to CSL_SERDES_LOOPBACK_DISABLED (serdes_diag_platform.h file)

1) My question is about the 2nd modification:

The way item 6 is written seems to me not that clear.

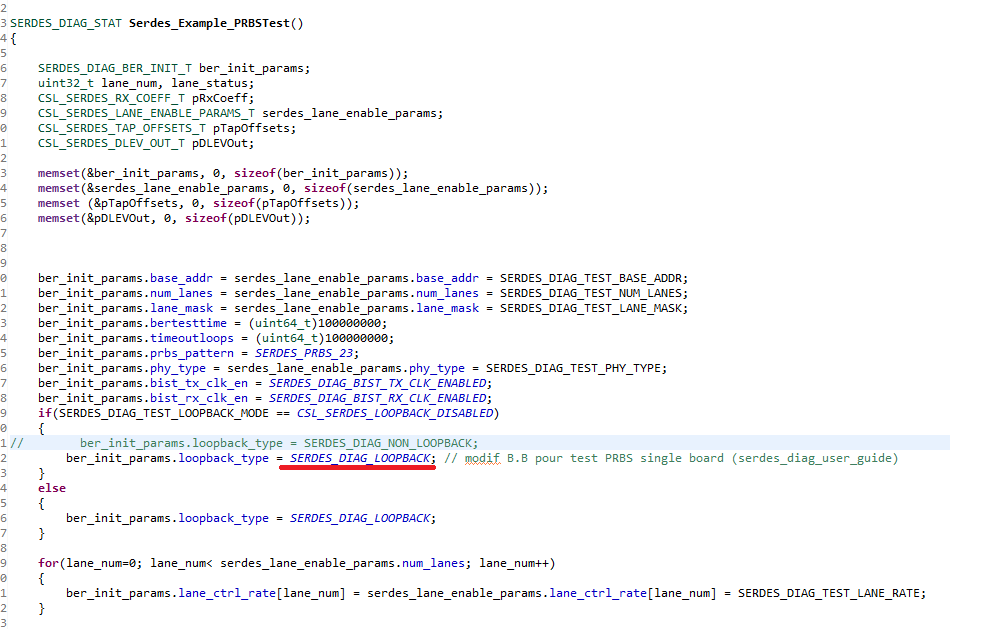

Inside the "serdes_diag_test.c" file I only found the "ber_init_params.loopback_type" once, and it is inside an "if" operation.

I did the following modification (see red underline)and want to know if this is what is expected from the user_guide :

(This forces "ber_init_params.loopback_type" to SERDES_DIAG_LOOPBACK whatever the SERDES_DIAG_TEST_LOOPBACK_MODE is)

2) another subsidiary question is to know to force TX side of the 66ak2h14 to also generate pure PRBS23 pattern. (even if no loopback exists outside)

with best regards,

Bruno