Other Parts Discussed in Thread: TDA4VM, TDA4VL, TDA4VH, DRA829

Part Numbers: TDA4VM/TDA4VH/TDA4VL

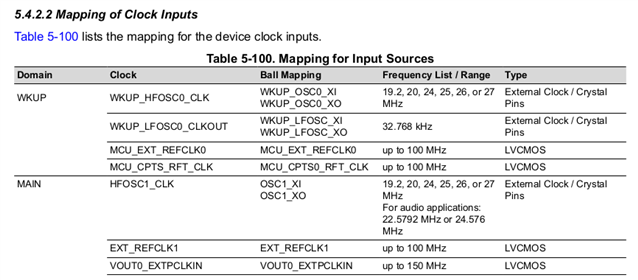

Referencing TRM DRA829/TDA4VM Technical Reference Manual (Rev. C) SPRUIL1C the below table can be seen. Is the external clock for HFOSC1_CLK required?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

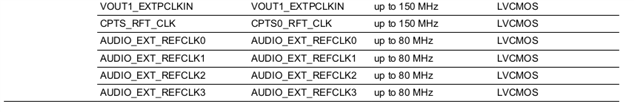

As listed in the table above:

Additionally, there is a low frequency external oscillator source for the WKUP domain LFOSC that is primarily to provide an accurate low frequency clock for use during lower power/sleep modes.

Is HFOSC1 External Oscillator required?

The SoC provides the option for two separate external oscillators for the Main(OSC1) and MCU(OSC0) domain to support customers who might use the SoC in mixed critical applications. This ensures that in the case of failure in one of the external oscillators, the other domain will remain functional and thus avoiding 'common cause failures' in using a single crystal for the whole SoC.

Having two external oscillators is not a “Hard Requirement” for safety. The chip is architected to be able to function on a single OSC(OSC0) for the entire MCU and Main domain and even if there is a fault in Main domain, the MCU domain can continue to operate using the OSC0. It is up to the system integrator to decide if a single or two crystal needs to be used in the specific application use-case. Some customers prefer using two separate OSC for MCU and Main domain, others choose one OSC for both MCU and Main domain.

Safety mechanisms for HFOSC0 / MCU Domain

MCU domain relies only on HFOSC0 and failure of HFOSC0 is result in loss of functionality of the SoC. Which is why it has the special clock loss detection and auto switch-over to CLK_12M_RC. This allows MCU domain to continue to function at the slow clock rate to allow system to get into a safe state. The error is routed to the WKUP ESM module and to the external error pin is asserted low, which is connected to an external monitoring circuit or PMIC. The PMIC should be used to put the TDA4VM to a safe state.

Safety mechanisms for HFOSC1 / Main Domain

A failure of HFOSC1 external oscillator (if used), does not directly affect MCU domain. DCC can be used to flag a safety error to MCU domain processor (or whatever portion of it is using HFOSC1) and MCU Domain can shut down, restart, or transition into a system safe state.

Safety mechanisms for LFOSC

DCC can be configured to detect failure of LFOSC as well.