Hi

I have modified the stock omap2_mcspi.c driver for the DM8148 to enable EDMA transfers using the fifo.

The DM8148 is still configured as a single channel master in receive only mode, with a word length of 8 bits and is effectively just reading data from the slave device, no data ever flows in the other direction.

My requirement is to send data at 30Mb/s over this link at 48MHz clock frequency which means a utilisation of about 62.5% but I'm seeing an unusual delay between bytes transferred even when using the fifo.

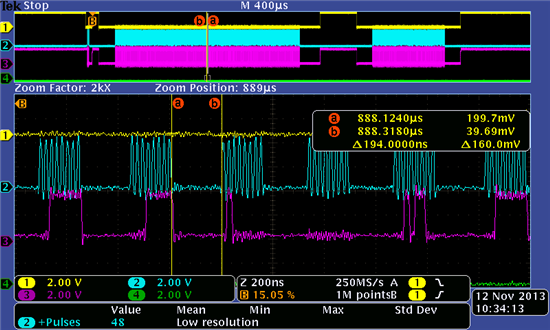

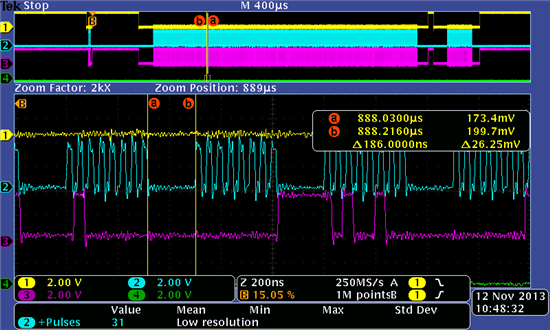

The attached images are taken from the scope

The CS is yellow

The SCLK is blue

The MISO is magenta

The first shows part of a transfer at 48MHz showing a delay of 194ns between each 8 bit transfer which in turn takes 167ns, so each byte takes 167+194 = 361ns to transfer with only 46% (167/361*100%) utilisation i.e. 48*0.46 = 22Mb/s

The first shows part of a transfer at 24MHz showing a delay of 186ns between each 8 bit transfer which in turn takes 333ns, so each byte takes 333+186 = 419ns to transfer with only 79.5% (333/419*100%) utilisation i.e. 24*0.795 = 19Mb/s

As you can see, doubling the clock speed gives a minimal increase in useable SPI bandwidth due to the large delay between bytes.

I considered changing the word length and using turbo mode but the other side of the link only supports 8 bit transfers (although it fully supports back to back transfers i.e. no gaps between bytes) but as luck would have it the 32bit data comes out at the DM8148 side in the wrong endianess and I don't have the cpu power available to continually byte swap 30Mb/s of data :-(

So I guess my questions are this

1. Is this normal or can I get rid of it some how?

2. Is there anything I can do to get the DM8148 to do back to back reads in 8 bit mode?

3. Is there any way to get the EDMA to do the byte swapping for free if I chose the 32 bit route?

4. Anything?

Thanks in advance

Robert McGowan