Dear Folks and TI specialist:

A.

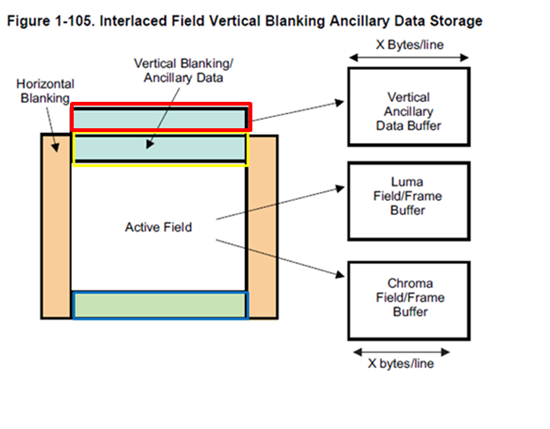

I encounter the problem about putting data to Vertical Blanking Interval(VBI). I try to put data on the VBI but I found sometime the extracted frame size(log is from 8148) are not correct.

Ex: video format is 720p59.94. the extracted frame size should be always video frame size: 1280x720 and VBI frame size:1280x30. But I found the frame size is sometime video frame size: 1280x720 and VBI frame size: 1280x15. The VBI frame size is always not correct.

(P.S The 8148 VIP port setting is “16 bit 4:2:2 YCbCr embedded sync mode”.)

[m3vpss ] | Total Even Odd Total Even Odd Min / Max Min / Max Dropped Fid Repeat Frame Error Y/C

[m3vpss ] CH | Fields Fields Fields FPS FPS FPS Width Height Fields Count (Desc Error Y/C)

[m3vpss ] ------------------------------------------------------------------------------------------------------------

[m3vpss ] 000 | 682 682 0 62 62 0 1280 / 1280 720 / 720 1 0 0/0 (0/0)

[m3vpss ] 010 | 683 683 0 62 62 0 65535 / 1 15 / 15 1 0 0/0 (0/0)

I think the reason is

- putted data sequence should not be FF, 00, 00

- Based on my test, the latest byte before EAV pattern should not be 00(h) or FF(h).

I want to know if anyone have the experience about this and can help me confirm if my reason is right about putting data on the VBI limitation .

B.

We have been considered to use 16 bit 4:2:2 YCbCr discrete sync mode but I have one consideration. I think the 16 bit YCbCr discrete sync mode implementation need to be taken more time because I need to support all video format and sync timing are all not the same. (I mean FPGA need support H_sync/V_SYNC/de/Field timing for all video formats and the timing need to follow CEA861.)

But after study HDVPSS user guide, seem the implementation is not very hard because 8148 VIP module receipt rule is easier for me.

Seem I only need to parse XYZ word in the SAV/EAV pattern and based on the parsed result (get F, V, H value) to assign H_sync/V_SYNC/de/Field value.(and delay video stream with parsing period).

The same as A.

I want to know if anyone have the experience about this and can give me some suggestion.

C.

In addition of (A and B), I also want to hope anyone can provide the other ideas for resolving the problem.

Thank you!!!

Environment:

DM8148 is my device and use VIP0 to receive video data(BT1120 or BT656). The VIP source device is FPGA. The connection is YcbCr 12bit 4:2:2 embedded sync mode.