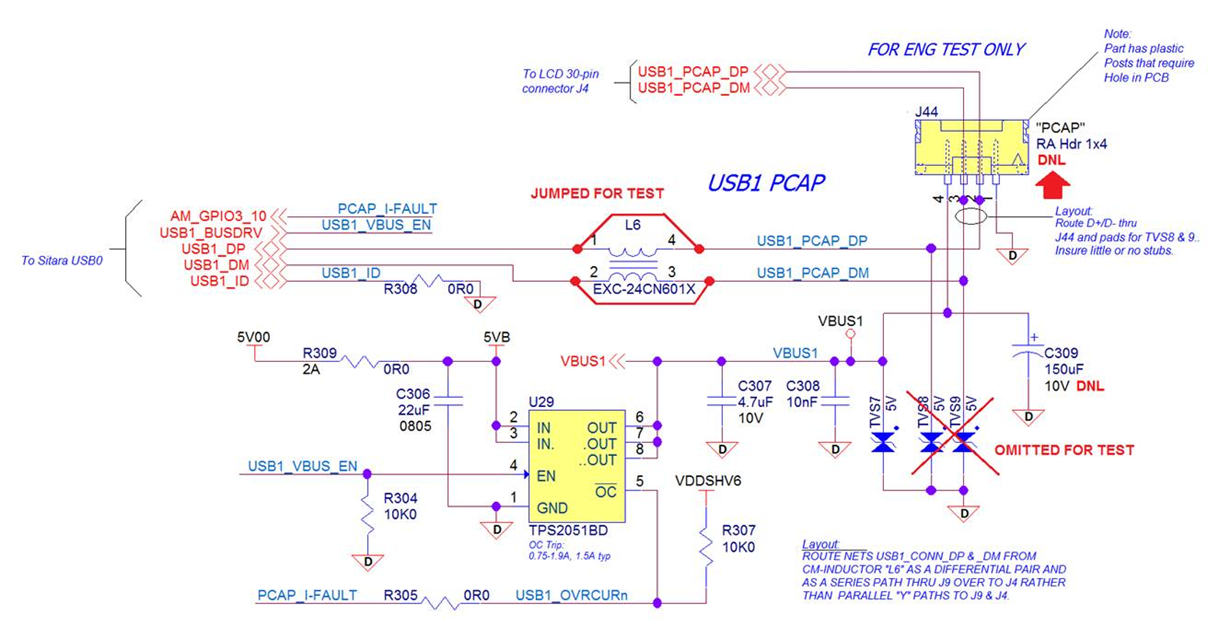

We are debugging a problem with our touchscreens intermittently not coming up.

We need some pretty detailed help on the behavior of the usb controller in the sitara.

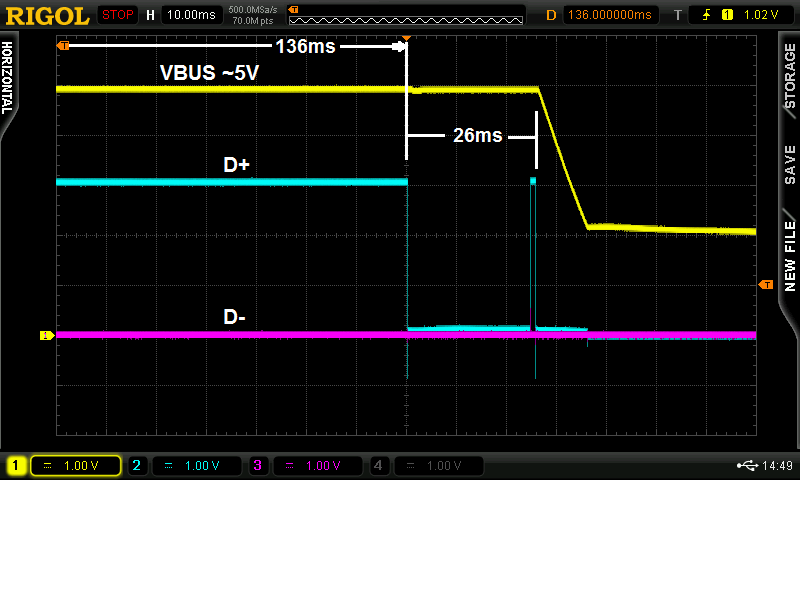

The touch screen devices are full-speed usb. After releasing reset after full speed detection, it looks like there is a problem where SOF does not happen when it fails. Sometimes it works and sends the SOF.

When it fails, D+ goes high, but no signaling happens, and then the sitara usb controller disables vbus on its own so we think it is detecting some error.

While trying to investigate this, we found this write up (from total phase website)

To accommodate the high-speed signaling levels and speeds, both hosts and devices use termination resistors. In addition, during the high-speed handshake, the device must release its full-speed pull-up resistor. But during the high-speed handshake, often times the host will activate its termination resistors before the device releases its full-speed pull-up resistor. In these situations the host may not be able to pull the D+ line below the threshold level of its high-speed receivers. This may cause the host to see a spurious Chirp J (dubbed a Tiny J) on the lines. This is an artifact on the bus due to the voltage divider effect between the device’s 1.5 Kohm pull-up resistor and the host’s 45 ohm termination resistor. Hosts and devices must be robust against this situation. Once the device has switched to high-speed operation the Tiny J will no longer be present, since the device will have released its pull-up resistor.

We don't have a high speed device, so this may not be it, but we seek the Tiny J on the total phase

sniffer prior to losing vbus in the failure case.

We need guidance on this. Is there any configurable timeout related to this on the controller side to delay whatever check it is doing after the reset is released that causes it to disable vbus? Even with the documentation, it is difficult to determine this.