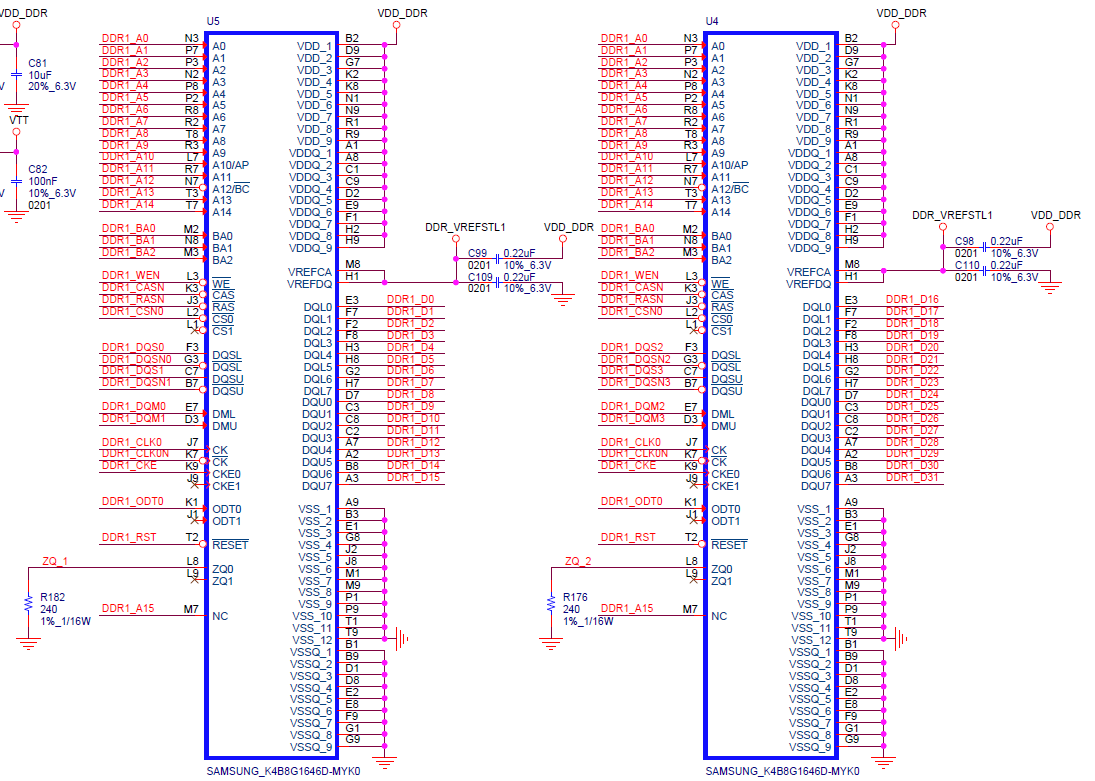

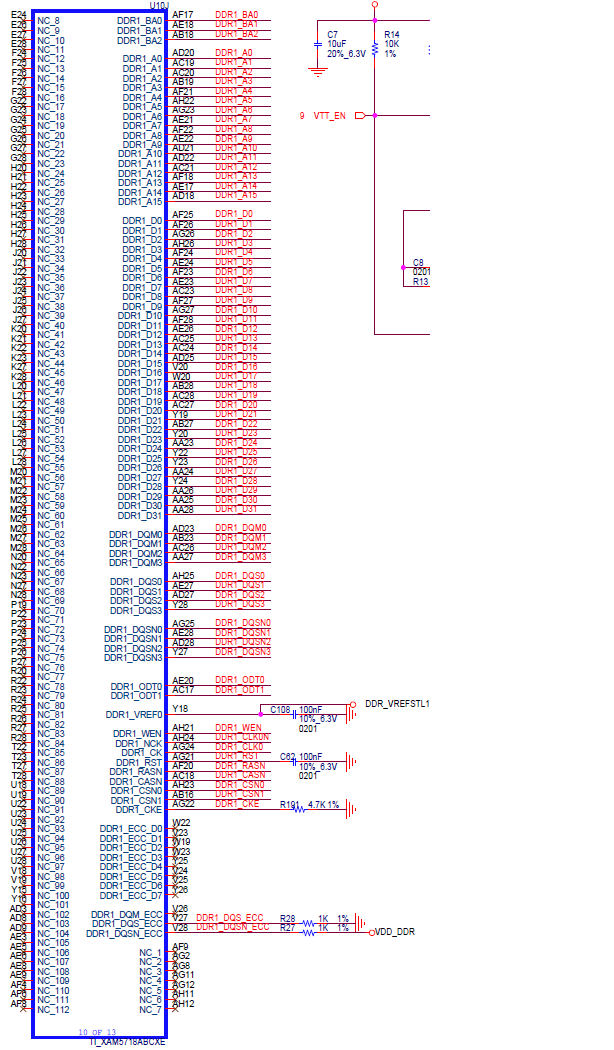

My customer use 2 pcs x16bit 8Bit DDR3 memory Dual-Die DDR3 on AM5718, got abnormal result, access 0x80000000-0xBFFFFFFF is right, access 0xC0000000-0xD0000000 also right, but access across 0xB0000000-0xD0000000 result system hang, seems the range across dual die, I searched e2e got AM437x doesn't support dual die, but not sure AM571x.

In datasheet sprs919k page 5 revision history: Dual-Rank memory support is removed.

Are Dual-die and Dual-Rank same thing?

Is dual-die is support, please let us know what need to be set to enable dual-die support.