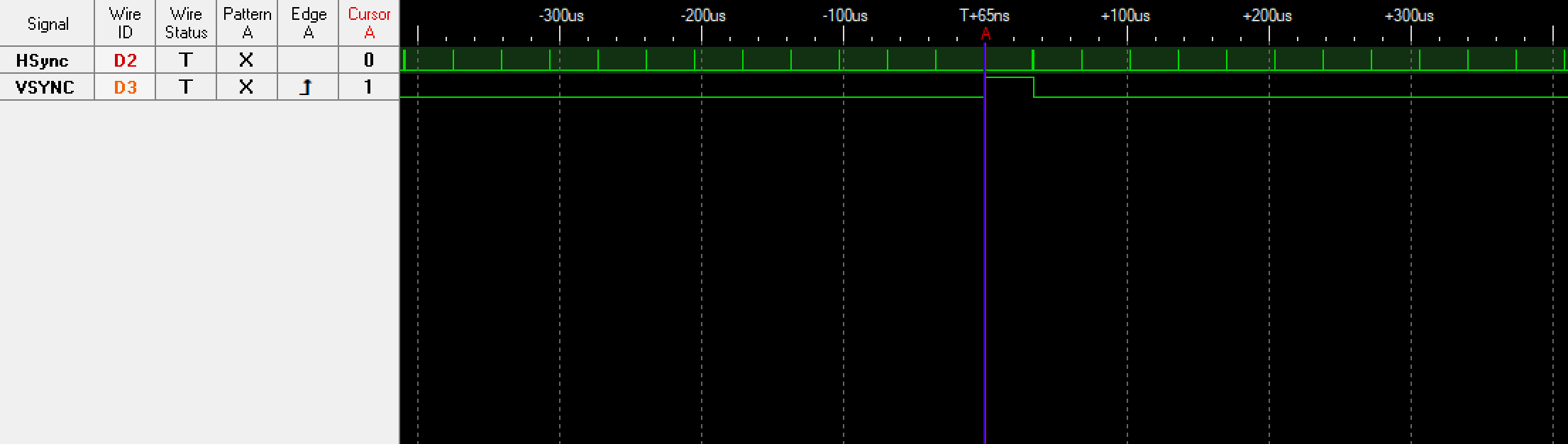

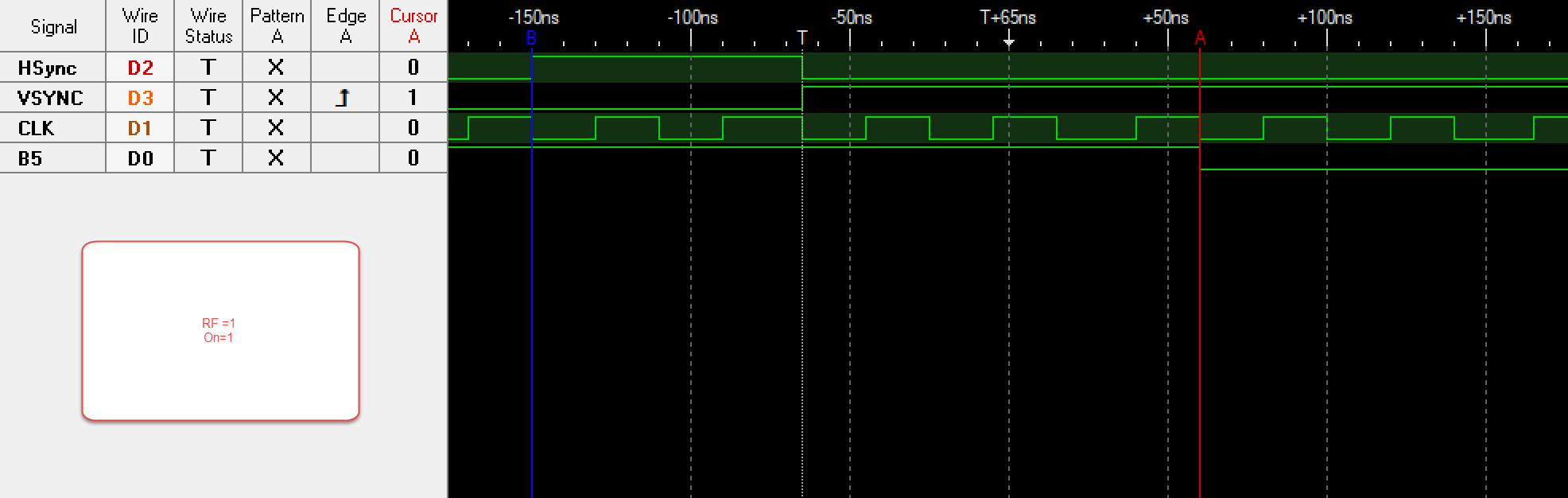

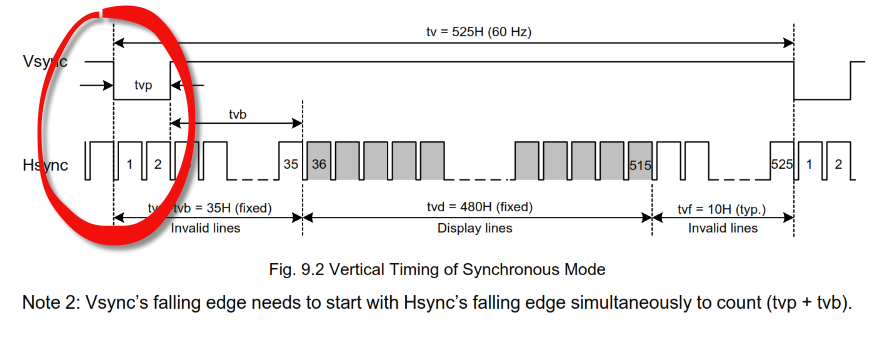

After successfully interfacing several LCD displays, I am having trouble with one particular interface. The display requires that HSync and VSync fall simultaneously.

I is there any way to configure the chip to do this? I have tried various combinations of Timing2 register. The logic analyzer confirms all other signals are correct.