Dear community,

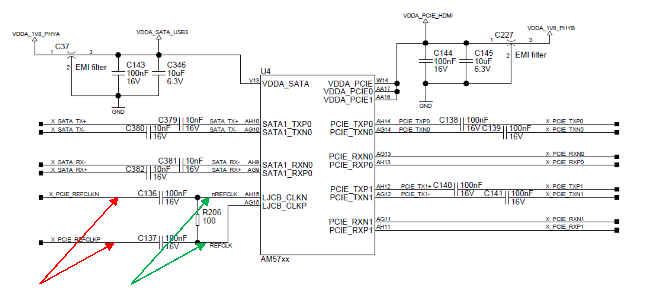

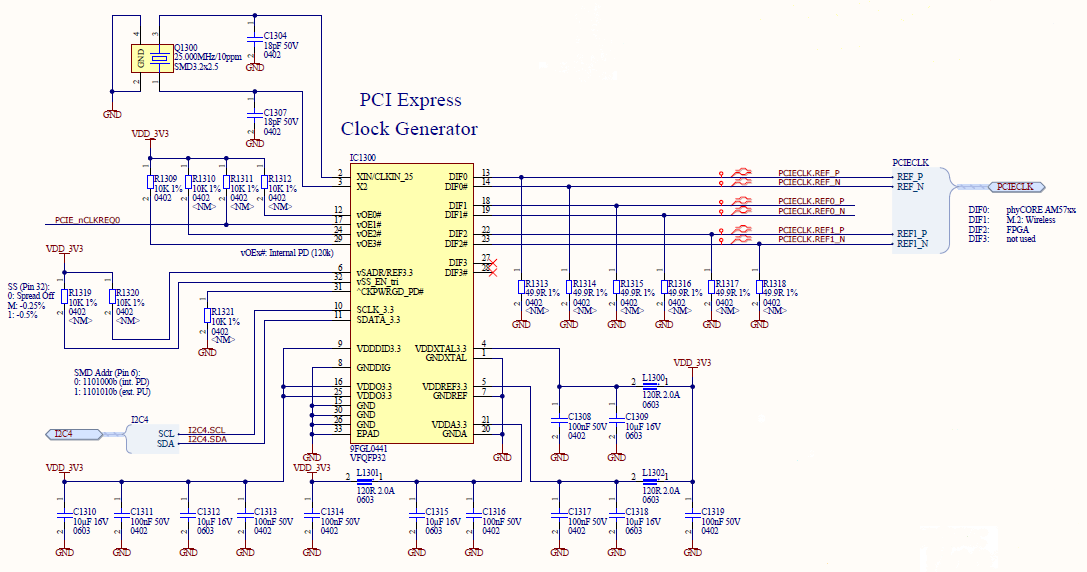

we are using PCIe on our custom Board to communicate with a standard Intel Wifi-card and our custom FPGA. The clock is generated by a 9FGL0441 PCIe clock generator device.

Part of our hardware-test was the evaluation of the signal integrity of the PCIe clocks to:

- WIFI-card

- FPGA

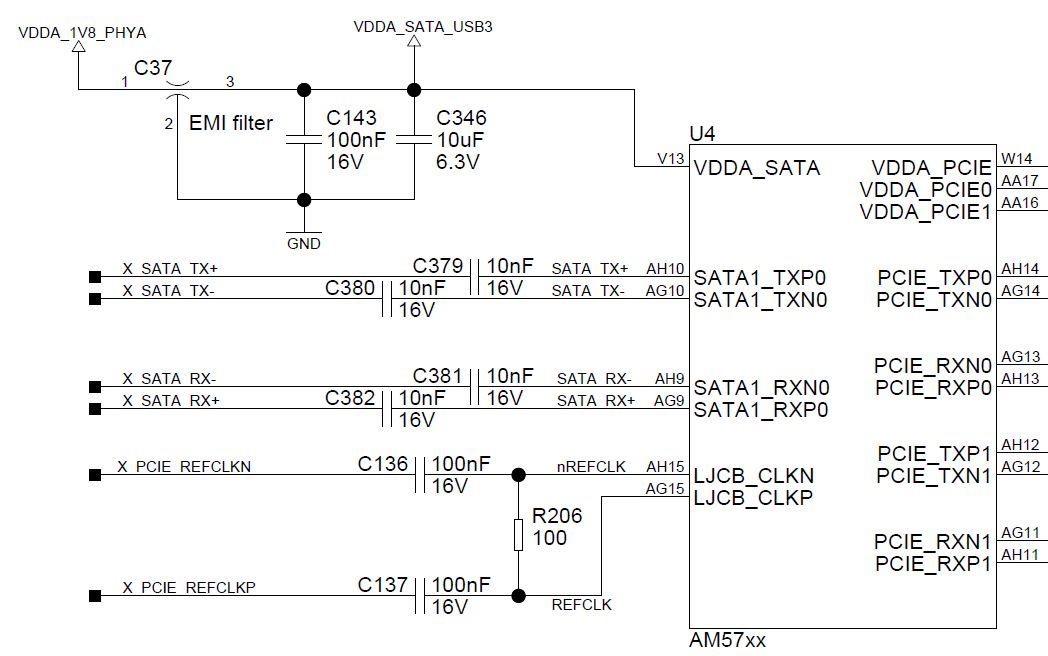

- AM5728

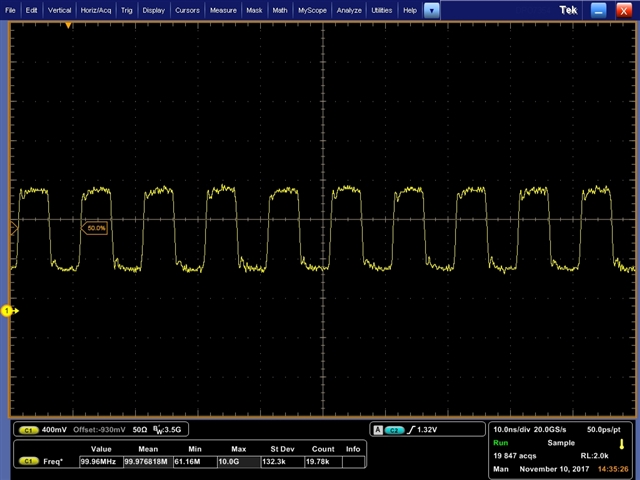

Measurements have been executed with a LeCroy SDA760Zi-A 6Ghz scope, using active differential probes with 6GHz bandwidth.

- The clocks to WIFI and FPGA showed no/small signal integrity issues.

- But the clock to the AM5728 CPU showed massive problems. Nevertheless, communication with WIFI-card and FPGA is working!

We did the same measurement on the AM5728-IDK and saw a similar effect.

The attached pictures show the clock measurement right after startup and after some uptime. No difference if the device stays in u-boot or has a fully booted Linux.

Has anybody else observed this? Currently we don't experience problems but we want to make sure this does not become a problem when we put this into a product.

Regards,

Michael