Tool/software: Code Composer Studio

Hello everybody,

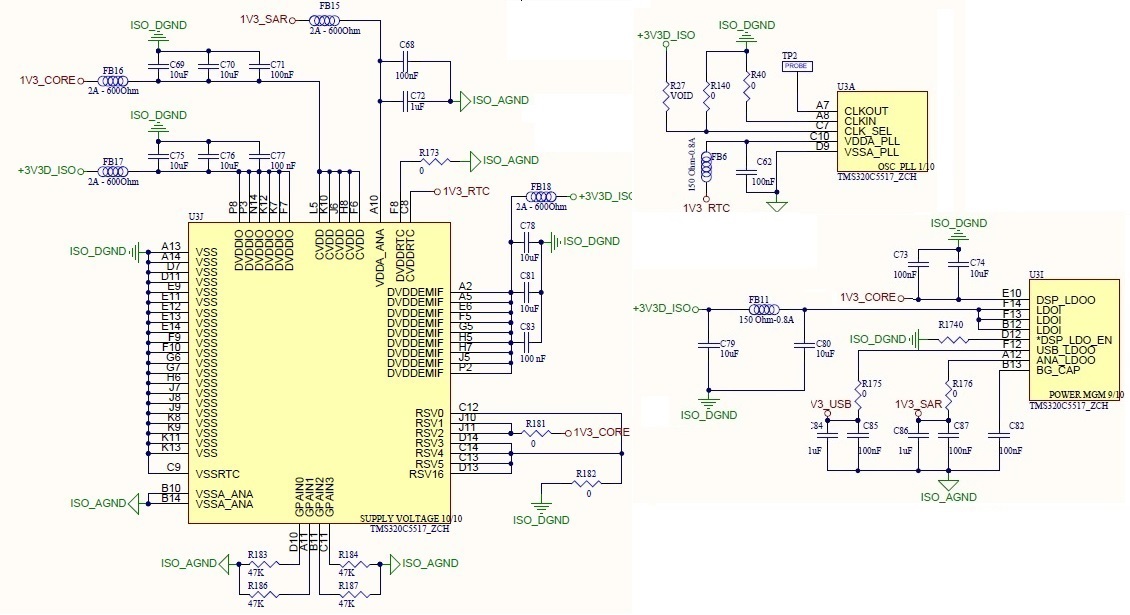

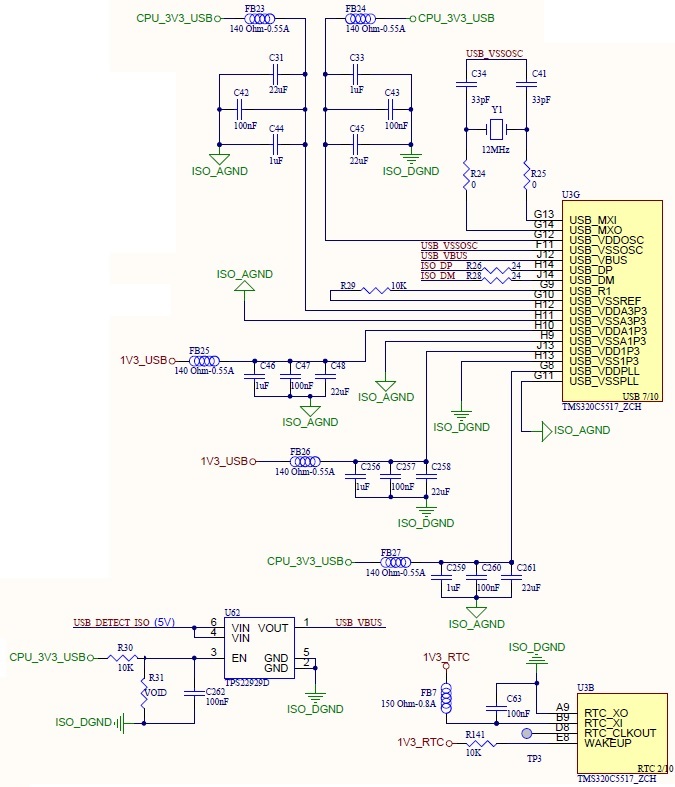

we developed a board TMS320C5517 provided with 1,3V core and 3.3V I/O.

DSP power related schematics are attached.

We have a problem related to DSP LDO outputs (1V3_USB,1V3_SAR,1V3_CORE),

which on certain circustances simultaneously drop from the nominal level of 1,3V to about 1,0 V or less,

which is largely under specifications, and we believe could spoil the DSP.

First of all, in general what this voltage drop could mean ?

Which feature of the board could effect this internally generated voltages ?

Now here we explain the circumstances.

DSP is asynchronous EMIF interfaced to a FPGA, which in turn is the master for some slave ADCs.

When the FPGA is driving the ADCs control signal (MCLK,LRCLK,SCLK), as soon the ADCs are removed from Reset

all the DSP LCD outputs drop to 1,0 V or less: LDO outputs return to regular 1,3V as soon the ADCs are kept in Reset.

The problem is also not present if we remove the ADCs from the board...

Please note that no direct digital HW interface exist between the ADCs and DSP; moreover in our tests,

we prevent DSP from driving the EMIF interface to FPGA.

LDO dropout occour even if we stop the software (using a breakpoint) and we configure all the GPIO as inputs.

EBSR register is configured as follow:

GpioStatus = SYS_setEBSR(CSL_EBSR_FIELD_PPMODE,CSL_EBSR_PPMODE_1);

GpioStatus |= SYS_setEBSR(CSL_EBSR_FIELD_SP0MODE,CSL_EBSR_SP0MODE_3);

GpioStatus |= SYS_setEBSR(CSL_EBSR_FIELD_SP1MODE,CSL_EBSR_SP1MODE_2);

GpioStatus |= SYS_setEBSR(CSL_EBSR_FIELD_A15MODE,CSL_EBSR_A_MODE_0);

GpioStatus |= SYS_setEBSR(CSL_EBSR_FIELD_A16MODE,CSL_EBSR_A_MODE_0);

GpioStatus |= SYS_setEBSR(CSL_EBSR_FIELD_A17MODE,CSL_EBSR_A_MODE_0);

GpioStatus |= SYS_setEBSR(CSL_EBSR_FIELD_A18MODE,CSL_EBSR_A_MODE_0);

GpioStatus |= SYS_setEBSR(CSL_EBSR_FIELD_A19MODE,CSL_EBSR_A_MODE_0);

GpioStatus |= SYS_setEBSR(CSL_EBSR_FIELD_A20MODE,CSL_EBSR_A_MODE_0);

The 3V3D_ISO voltage providing the input at LDOI is stable to 3.3V, with a current draw of 140mA (3.3V regulator max current 500mA)

Measurig the current draw at the LDOs outputs we have:

DSP_LDOO: 24mA (max)

USB_LDOO: <1mA

ANA_LDOO: <1mA

1V3_RTC voltage is stable, with no drop below 1.3V.

If we drive the RESET pin low while the ADCs are on and the LDO voltage is below 1V, DSP_LDOO, USB_LDOO, ANA_LDOO go back to 1.3V.

I also tried to exclude USB influence by removing R175, with no better results.

On these circumstances, what do you think could cause the LDOs outputs drop?

Could a GPIO conflict cause an LDO voltage drop?

Do not esitate to request us more informations.

Thank you for your attention.