Other Parts Discussed in Thread: STRIKE

Hi Sir

we used AM3352 for development and have some issues which need your suggestion.

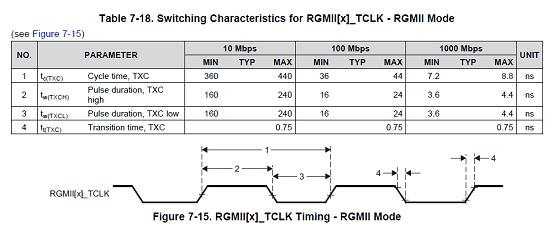

a. for item4 - TXC, we measured the time is 1.5ns but the max. time of spec is 0.75.

any improvement method or could you confirm it is ok?

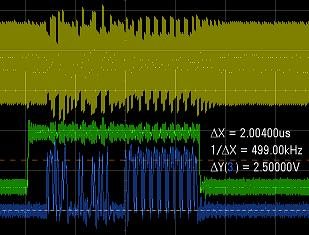

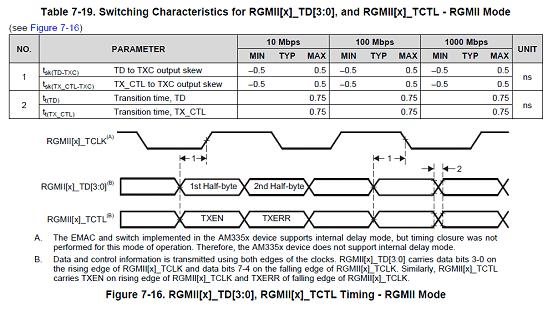

2. In RGMII spec, the TCTL signal will change with the data signal at the same time.

We measure the signal of TCTL is high level during data transmission.

you can see below photo. the green line is the TCTL signal. Could you confirm it is ok or not?