Tool/software: Linux

Hi SIr

We followed AM335x SK-EVM design and connect PMIC's VRTC to RTC module of CPU.

There is no problem if we used external power adapter to power on the system. It can boot successfully.

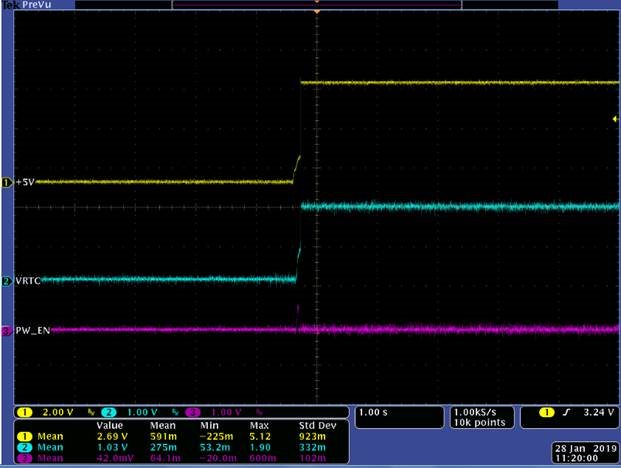

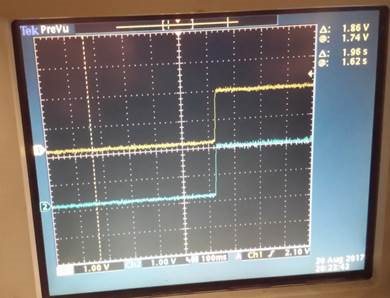

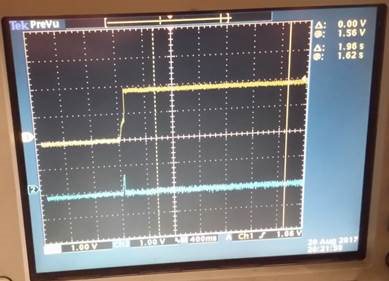

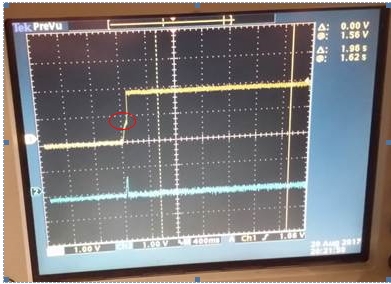

If we connect our CPU MB to another power board, we found the waveform about VRTC of PMIC as below which may cause PMIC_POWER_EN not be able to set high.

Does TI have any spec about the rising time of VDDS_RTC or CPU RTC's module ? or above VRTC's waveform has any risk to CPU which cause PMIC_POWER_EN abnormally ?

please advise

BR

Yimin