Tool/software: TI-RTOS

Hi All,

I am working on TDA2PX Custom board, using Vision SDK 3.5. I went through a document DSS BT656 Workaround for TDA2x.pdf for making the ADV7393 encoder work on the custom board.

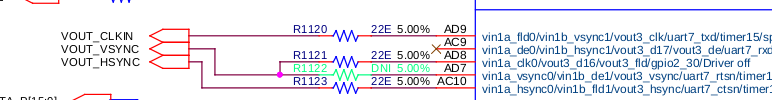

The CLK_IN,HSYNC ,VSYNC and D0-D15 are input to the encoder. The DAC1 output from ADV7393 is connected to ADA4430 filter. The output from the filter is connected to a fakra connector. We connect the signal from fakra to an Analog output device.

For testing purpose I have done the following changes in the chains_common.c.

IN the menu I choose System Settings--> Display Settings--> Selecting 1 for selecting CHAINS_DISPLAY_TYPE_LCD_7_INCH

In the file vision_sdk/apps/src/rtos/usecases/common/chains_common.c

if(displayType == CHAINS_DISPLAY_TYPE_LCD_7_INCH)

{

pPrm->deviceId = DISPLAYCTRL_LINK_USE_LCD;

/* Changing the display port to LCD3 */

pVInfo->vencId = SYSTEM_DCTRL_DSS_VENC_LCD3; //changed from SYSTEM_DCTRL_DSS_VENC_LCD1 as display output is on LCD3

pVInfo->outputPort = SYSTEM_DCTRL_DSS_DPI3_OUTPUT; // changed from SYSTEM_DCTRL_DSS_DPI1_OUTPUT

pVInfo->vencOutputInfo.dataFormat = SYSTEM_DF_BGR16_565; // Changed from SYSTEM_DF_RGB24_888

pVInfo->vencOutputInfo.dvoFormat = SYSTEM_DCTRL_DVOFMT_GENERIC_DISCSYNC;

pVInfo->vencOutputInfo.videoIfWidth = SYSTEM_VIFW_16BIT; //Changed from SYSTEM_VIFW_24BIT

pVInfo->vencOutputInfo.pixelClkPolarity = SYSTEM_DCTRL_POLARITY_ACT_HIGH;

pVInfo->vencOutputInfo.aFmt = SYSTEM_DCTRL_A_OUTPUT_MAX;

/* Configure overlay params */

ovlyPrms->vencId = SYSTEM_DCTRL_DSS_VENC_LCD3; //SYSTEM_DCTRL_DSS_VENC_LCD1

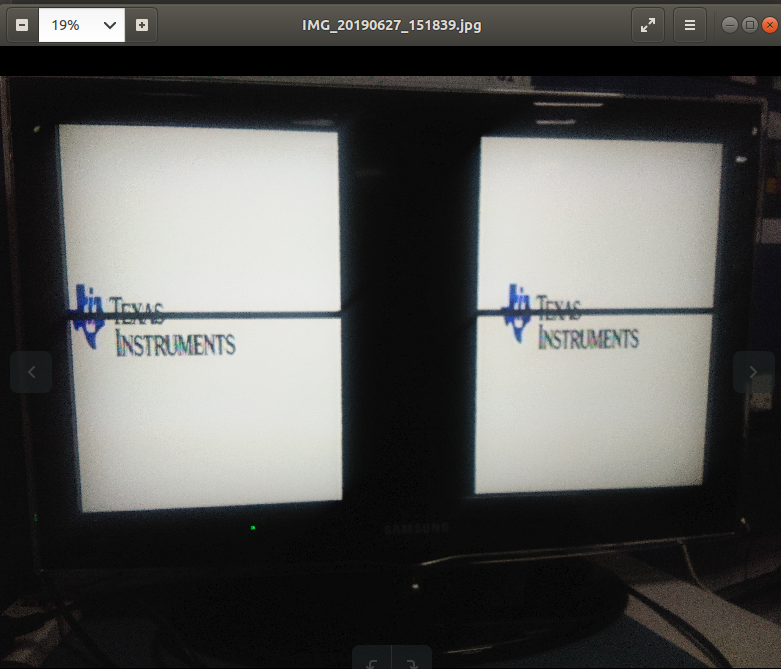

With the above changes I got 27MHz output on the clock, then I tried adding pattern generation from the ADV7393 side. I am getting a flickering display.

After reading the DSS BT656 Workaround for TDA2x.pdf I added TDM configuration.

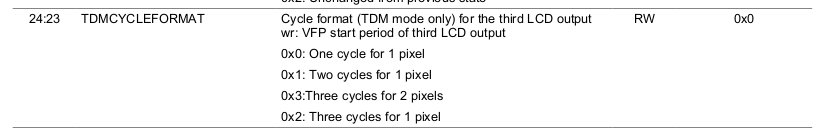

DISPC_CONTROL1.TDMENABLE = 0x1: TDM enabled

DISPC_CONTROL1.TDMPARALLELMODE = 0x3: 16-bit parallel output selected

DISPC_CONTROL1.TDMCYCLEFORMAT = 0x1: 2 cycles for 1 pixel

DISPC_DATA1_CYCLE1 = 16

DISPC_DATA1_CYCLE2 = 0

DISPC_DATA1_CYCLE3 = 0

But with the changes for TDM mode resulted in ON/OFF of the display along with flickering. So I removed them again.

Am I missing anything in configuration deom TDA2P Side.

Regards,

Deepika