Other Parts Discussed in Thread: SYSBIOS

Hi everyone,

I am doing a test in which DSP core 0 and DSP core 1 have each a specific DDR area. DSP core 1 can't access DDR area of DSP core0. I am trying to handle exceptions with errors when occurs. I already done this with MPPA (it works) but with MPAX, I can't handle the exception.

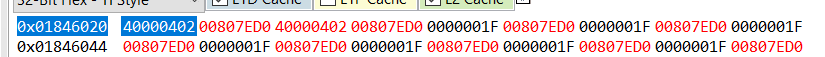

However, when DSP core 1 trying to access DDR area of DSP core 0 , it can't and the error is reported through XMPFAR and XMPFSR of DSP core1.

This is my configuration:

/* Exception */ Exception.enableExternalMPC = true; Exception.enablePrint = false; Exception.useInternalBuffer = true; Exception.exceptionHook = "&myExcep_handler"; Exception.externalHook = "&myExcep_handler_extn"; Exception.internalHook = "&myExcep_handler_intn"; Exception.nmiHook = "&myExcep_handler_nmi"; Exception.returnHook = null; /* Hw Interupt */ Hwi.enableException = true;

for (i=119; i<128; i++) { Exception_evtExpMaskEnable(i); }

Does anyone can help me ?

Best Regards,

François