Dear Professer,

I'm using PSDK 70_01_00.

I'm putting mcan_test program runs in MCU1_ 0, and view the print information from the remote log. Now my function calls in app_run.c:

void appRun()

{

appLogPrintf("APP: Run ... !!!\n");

/*loop to debug*/

#ifdef CPU_mcu1_0

#if 1

asm("test: nop");

asm(" nop");

asm(" b test ");

asm(" nop");

asm(" nop");

#endif

//appLogPrintf("Wait ... -----------------------!!!\n");

//appLogWaitMsecs(10000);

#endif

#if 1

#ifdef CPU_mcu1_0

appLogPrintf("Start can test ... -----------------------!!!\n");

canTest();

appLogPrintf("Start can test ... Done-----------------------!!!\n");

#endif

#endif

#if defined(ENABLE_IPC_ECHO_TEST) && defined(ENABLE_IPC)

appIpcEchoTestStart();

#endif

#if defined(ENABLE_TIOVX_HOST)

appMenuMain();

#endif

appLogPrintf("APP: Run ... Done !!!\n");

}

At present, there are the following problems:

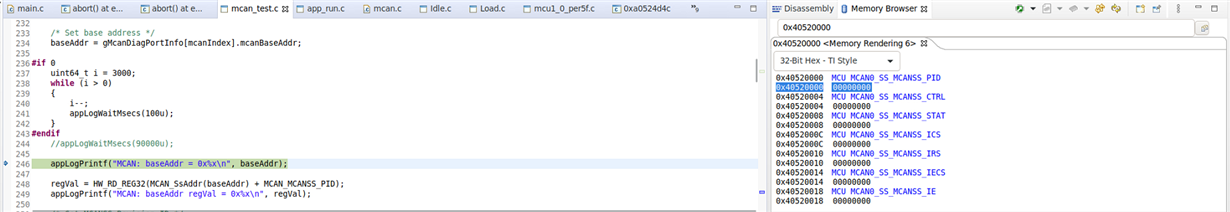

1. I use CCS debugging to find that the program can run at present, but when reading or writing registers, the program will terminate directly.

For example, in mcan_test.c:: MCAN_getRevisionId(baseAddr, &revId), the baseAddr is 0x40500000, when it calls HW_RD_REG32(), it will terminate at

static inline uint32_t HW_RD_REG32_RAW(uint32_t addr)

{

uint32_t regVal = *(volatile uint32_t *) ((uintptr_t) addr);

/* Donot call any functions after this. If required implement as macros */

HW_SYNC_BARRIER();

return (regVal);

}

This is the printed message of CCS at termination.

2. Occasionally, the register can be read and written successfully, and the program can run normally (only under CCS debugging). But most of the time, the program will report an error. Without CCS the program was never started successfully.

How to read and write register successfully?

Regards,

JJXie