Part Number: TDA4VM

Other Parts Discussed in Thread: DRA829,

Hi

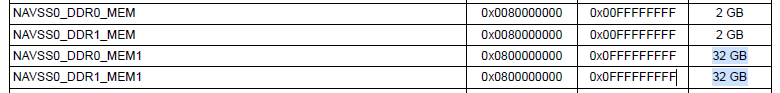

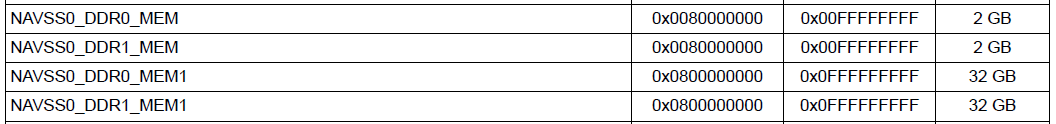

Access to DDR memory is limited by 2GB.

We want to be able to access 32GB area for this.

Please let me know how to do this.

■Remarks

\ti\ccs1011\ccs\ccs_base\emulation\gel\J721E_DRA829_TDA4VM\gel\J721E_DDR32SS

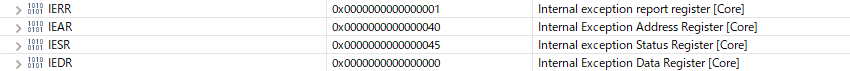

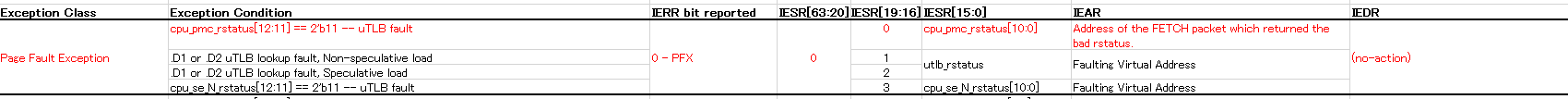

The file above only supports 32 bits.

→Requires a 64bit-compatible gel file.

Currently, NAVSS0_DDR1_MEM is used in the GEL file, but please provide a GEL file to use a 32GB map.