Hi,

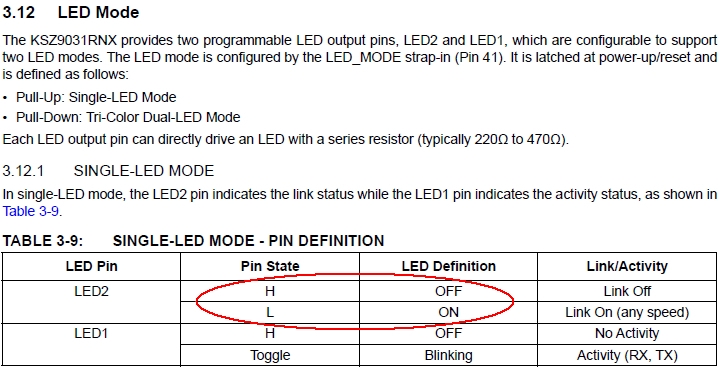

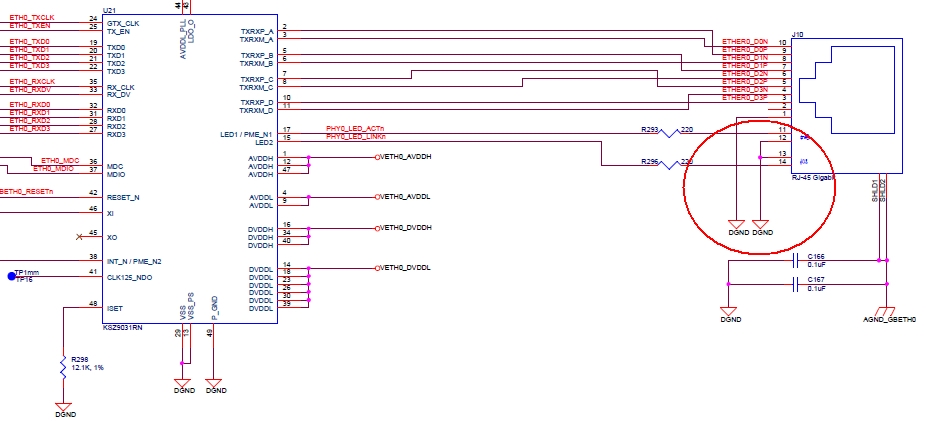

It seems that the LED polarity of the Gigabit Ethernet Link and Activity LED might be wrong on the AM571x IDK EVM (J12, U24 and J10, U21). KSZ9031RNX turns-on the LED's with a logic "L". I could not find a register in the PHY that can change polarity of the LED's.

Can someone from the EVM team please confirm or deny.

Thanks and best regards,

Patrick

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.