Part Number: TRF372017

Hi teams,

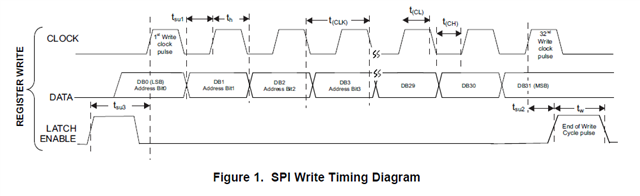

We want to use NXP Processor to control TRF372017, and let the Latch-Enable signal to notify TRF372017, as shown in the figure below:

But NXP Processor's SPI does not have a Latch-Enable Pin, is it possible to connect SPI CS to Latch-Enable and let CS (Always keep Hi, pull to Lo when data is to be transmitted) instead of Latch-Enable to transmit SPI data?

Thanks.