Hello

I would like to configure the ADC32RF80 for decimate by 16. I have been successfully using the ADC32RF80 for decimate by 4 and 8 in the following configuration:

Decimate by 4:

LMFS = 8422

PLL MODE = 20X

JESD MODE 0, 1, 2 = 1, 0, 0

RATIO = 2.5

Decimate by 8:

LMFS = 4421

PLL MODE = 20X

JESD MODE 0, 1, 2 = 1, 0, 0

RATIO = 2.5

I am trying to configure the ADC32RF80 for decimate by 16 so as to keep the RATIO = 2.5. This will simplify our firmware if the lane rate is the same for decimate by 4, 8 and 16. To do this, I am trying to configure the ADC32RF80 as follows:

Decimate by 16:

LMFS = 2441

PLL MODE = 40X

JESD MODE 0, 1, 2 = 2, 0, 0

RATIO = 2.5

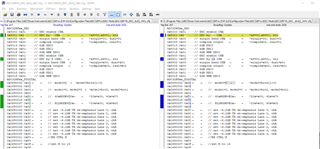

The following is the register writes relating to the JESD configuration and the DDC configuration. The options for decimate by 4 and 8 are commented out. As far as I can tell, all other register writes remain the same when changing decimation rate:

#define ADC_DEC_CHAN_A_DDC_EN 0x5000

#define ADC_DEC_CHAN_A_DECIM_FACTOR 0x5001

#define ADC_DEC_CHAN_A_DUAL_BAND_EN 0x5002

#define ADC_DEC_CHAN_A_REAL_OUT_EN 0x5005

#define ADC_DEC_CHAN_A_DDC_MUX 0x5006

#define ADC_DEC_CHAN_A_DDC0_NCO1_LSB 0x5007

#define ADC_DEC_CHAN_A_DDC0_NCO1_MSB 0x5008

#define ADC_DEC_CHAN_A_DDC0_NCO2_LSB 0x5009

#define ADC_DEC_CHAN_A_DDC0_NCO2_MSB 0x500A

#define ADC_DEC_CHAN_A_DDCO_NCO3_LSB 0x500B

#define ADC_DEC_CHAN_A_DDC0_NCO3_MSB 0x500C

#define ADC_DEC_CHAN_A_DDC1_NCO4_LSB 0x500D

#define ADC_DEC_CHAN_A_DDC1_NCO4_MSB 0x500E

#define ADC_DEC_CHAN_A_NCO_SEL_PIN 0x500F

#define ADC_DEC_CHAN_A_NCO_SEL 0x5010

#define ADC_DEC_CHAN_A_LMFC_RESET_MODE 0x5011

#define ADC_DEC_CHAN_A_DDC0_6DB_GAIN 0x5014

#define ADC_DEC_CHAN_A_DDC1_6DB_GAIN 0x5016

#define ADC_DEC_CHAN_A_DDC_DET_LAT 0x501E

#define ADC_DEC_CHAN_A_WBF_6DB_GAIN 0x501F

#define ADC_DEC_CHAN_B_DDC_EN 0x5800

#define ADC_DEC_CHAN_B_DECIM_FACTOR 0x5801

#define ADC_DEC_CHAN_B_DUAL_BAND_EN 0x5802

#define ADC_DEC_CHAN_B_REAL_OUT_EN 0x5805

#define ADC_DEC_CHAN_B_DDC_MUX 0x5806

#define ADC_DEC_CHAN_B_DDC0_NCO1_LSB 0x5807

#define ADC_DEC_CHAN_B_DDC0_NCO1_MSB 0x5808

#define ADC_DEC_CHAN_B_DDC0_NCO2_LSB 0x5809

#define ADC_DEC_CHAN_B_DDC0_NCO2_MSB 0x580A

#define ADC_DEC_CHAN_B_DDCO_NCO3_LSB 0x580B

#define ADC_DEC_CHAN_B_DDC0_NCO3_MSB 0x580C

#define ADC_DEC_CHAN_B_DDC1_NCO4_LSB 0x580D

#define ADC_DEC_CHAN_B_DDC1_NCO4_MSB 0x580E

#define ADC_DEC_CHAN_B_NCO_SEL_PIN 0x580F

#define ADC_DEC_CHAN_B_NCO_SEL 0x5810

#define ADC_DEC_CHAN_B_LMFC_RESET_MODE 0x5811

#define ADC_DEC_CHAN_B_DDC0_6DB_GAIN 0x5814

#define ADC_DEC_CHAN_B_DDC1_6DB_GAIN 0x5816

#define ADC_DEC_CHAN_B_DDC_DET_LAT 0x581E

#define ADC_DEC_CHAN_B_WBF_6DB_GAIN 0x581F

#define ADC_DIGITAL_BANK_PAGE_SEL_MSB 0x4004

#define ADC_DIGITAL_BANK_PAGE_SEL_MID 0x4003

#define ADC_DIGITAL_BANK_PAGE_SEL_LSB 0x4002

#define ADC_MAIN_DIG_PAGE_NQ_ZONE_EN 0x60A2

#define ADC_MAIN_DIG_DIG_RESET 0x6000

#define ADC_JESD_CHAN_A_CTRL_K 0x7001

#define ADC_JESD_CHAN_A_SYNC_REG 0x7002

#define ADC_JESD_CHAN_A_LINK_LAYER_TESTMODE 0x7003

#define ADC_JESD_CHAN_A_REL_ILA_SEQ 0x7004

#define ADC_JESD_CHAN_A_SCRAMBLE_EN 0x7006

#define ADC_JESD_CHAN_A_FRAMES_PER_MULTIFRAME 0x7007

#define ADC_JESD_CHAN_A_40X_MODE 0x7016

#define ADC_JESD_CHAN_A_LANE0_POL 0x7017

#define ADC_JESD_CHAN_A_SEL_EMP_LANE_0 0x7032

#define ADC_JESD_CHAN_A_SEL_EMP_LANE_1 0x7033

#define ADC_JESD_CHAN_A_SEL_EMP_LANE_2 0x7034

#define ADC_JESD_CHAN_A_SEL_EMP_LANE_3 0x7035

#define ADC_JESD_CHAN_A_CMOS_SYNCB 0x7036

#define ADC_JESD_CHAN_A_PLL_MODE 0x7037

#define ADC_JESD_CHAN_A_EN_CMOS_SYNCB 0x703C

#define ADC_JESD_CHAN_B_CTRL_K 0x6001

#define ADC_JESD_CHAN_B_SYNC_REG 0x6002

#define ADC_JESD_CHAN_B_LINK_LAYER_TESTMODE 0x6003

#define ADC_JESD_CHAN_B_REL_ILA_SEQ 0x6004

#define ADC_JESD_CHAN_B_SCRAMBLE_EN 0x6006

#define ADC_JESD_CHAN_B_FRAMES_PER_MULTIFRAME 0x6007

#define ADC_JESD_CHAN_B_40X_MODE 0x6016

#define ADC_JESD_CHAN_B_LANE0_POL 0x6017

#define ADC_JESD_CHAN_B_SEL_EMP_LANE_0 0x6032

#define ADC_JESD_CHAN_B_SEL_EMP_LANE_1 0x6033

#define ADC_JESD_CHAN_B_SEL_EMP_LANE_2 0x6034

#define ADC_JESD_CHAN_B_SEL_EMP_LANE_3 0x6035

#define ADC_JESD_CHAN_B_CMOS_SYNCB 0x6036

#define ADC_JESD_CHAN_B_PLL_MODE 0x6037

#define ADC_JESD_CHAN_B_EN_CMOS_SYNCB 0x603C

// DIGITAL BANK

// MAIN JESD DIGITAL PAGE

ADC_DIGITAL_BANK_PAGE_SEL_LSB=0x00

ADC_DIGITAL_BANK_PAGE_SEL_MID=0x00

ADC_DIGITAL_BANK_PAGE_SEL_MSB=0x69

//ADC_JESD_CHAN_A_SYNC_REG=0x01 // DEC 4/8

ADC_JESD_CHAN_A_SYNC_REG=0x02 // DEC 16

//ADC_JESD_CHAN_B_SYNC_REG=0x01 // DEC 4/8

ADC_JESD_CHAN_B_SYNC_REG=0x02 // DEC 16

//ADC_JESD_CHAN_A_PLL_MODE=0x00 // DEC 4/8

//ADC_JESD_CHAN_B_PLL_MODE=0x00 // DEC 4/8

ADC_JESD_CHAN_A_PLL_MODE=0x02 // DEC 16

ADC_JESD_CHAN_B_PLL_MODE=0x02 // DEC 16

ADC_JESD_CHAN_A_40X_MODE=0x70 // DEC 16

ADC_JESD_CHAN_B_40X_MODE=0x70 // DEC 16

ADC_JESD_CHAN_A_CTRL_K=0x80

ADC_JESD_CHAN_B_CTRL_K=0x80

ADC_JESD_CHAN_A_FRAMES_PER_MULTIFRAME=0x1F

ADC_JESD_CHAN_B_FRAMES_PER_MULTIFRAME=0x1F

ADC_JESD_CHAN_A_LINK_LAYER_TESTMODE=0x00

ADC_JESD_CHAN_B_LINK_LAYER_TESTMODE=0x00

ADC_JESD_CHAN_A_SEL_EMP_LANE_0=0x3C

ADC_JESD_CHAN_B_SEL_EMP_LANE_0=0x3C

ADC_JESD_CHAN_A_SEL_EMP_LANE_1=0x3C

ADC_JESD_CHAN_B_SEL_EMP_LANE_1=0x3C

ADC_JESD_CHAN_A_SEL_EMP_LANE_2=0x3C

ADC_JESD_CHAN_B_SEL_EMP_LANE_2=0x3C

ADC_JESD_CHAN_A_SEL_EMP_LANE_3=0x3C

ADC_JESD_CHAN_B_SEL_EMP_LANE_3=0x3C

ADC_JESD_CHAN_A_CMOS_SYNCB=0x40 // SET FOR SINGLE ENDED SYNC

ADC_JESD_CHAN_A_EN_CMOS_SYNCB=0x01 // SET FOR SINGLE ENDED SYNC

// DIGITAL BANK

// DIRECT ADDRESSING

// DDC PAGES

ADC_DEC_CHAN_A_DDC_EN=0x01

//ADC_DEC_CHAN_A_DECIM_FACTOR=0x00 // DEC 4

//ADC_DEC_CHAN_A_DECIM_FACTOR=0x02 // DEC 8

ADC_DEC_CHAN_A_DECIM_FACTOR=0x07 // DEC 16

ADC_DEC_CHAN_A_DUAL_BAND_EN=0x00 // SINGLE BAND

ADC_DEC_CHAN_A_REAL_OUT_EN=0x00

ADC_DEC_CHAN_A_DDC_MUX=0x00

ADC_DEC_CHAN_A_DDC0_NCO1_LSB=0x55 // NCO1 = 21845 = 1GHz CF

ADC_DEC_CHAN_A_DDC0_NCO1_MSB=0x55

ADC_DEC_CHAN_A_DDC0_NCO2_LSB=0x00

ADC_DEC_CHAN_A_DDC0_NCO2_MSB=0x00

ADC_DEC_CHAN_A_DDCO_NCO3_LSB=0x00

ADC_DEC_CHAN_A_DDC0_NCO3_MSB=0x00

ADC_DEC_CHAN_A_DDC1_NCO4_LSB=0x00

ADC_DEC_CHAN_A_DDC1_NCO4_MSB=0x00

ADC_DEC_CHAN_A_WBF_6DB_GAIN=0x01 // USING WB DDC SO ADD 6DB GAIN

ADC_DEC_CHAN_A_DDC0_6DB_GAIN=0x01

ADC_DEC_CHAN_A_DDC1_6DB_GAIN=0x01

ADC_DEC_CHAN_A_NCO_SEL_PIN=0x00 // NCO SELECTED THROUGH SPI

ADC_DEC_CHAN_A_NCO_SEL=0x00 // NCO 1 SELECTED

ADC_DEC_CHAN_A_LMFC_RESET_MODE=0x00 // ALL DDCS AND NCOS RESET WITH EVERY LMFC

//ADC_DEC_CHAN_A_DDC_DET_LAT=0x50 // ENSURE DETERMINISTIC LATENCY FOR DEC BY 4, DEC BY 8

ADC_DEC_CHAN_A_DDC_DET_LAT=0x20 // ENSURE DETERMINISTIC LATENCY FOR DEC BY 16

ADC_DEC_CHAN_B_DDC_EN=0x01

//ADC_DEC_CHAN_B_DECIM_FACTOR=0x00 // DEC 4

//ADC_DEC_CHAN_B_DECIM_FACTOR=0x02 // DEC 8

ADC_DEC_CHAN_B_DECIM_FACTOR=0x07 // DEC 16

ADC_DEC_CHAN_B_DUAL_BAND_EN=0x00 // SINGLE BAND

ADC_DEC_CHAN_B_REAL_OUT_EN=0x00

ADC_DEC_CHAN_B_DDC_MUX=0x00

ADC_DEC_CHAN_B_DDC0_NCO1_LSB=0x55 // NCO1 = 21845 = 1GHZ CF

ADC_DEC_CHAN_B_DDC0_NCO1_MSB=0x55

ADC_DEC_CHAN_B_DDC0_NCO2_LSB=0x00

ADC_DEC_CHAN_B_DDC0_NCO2_MSB=0x00

ADC_DEC_CHAN_B_DDCO_NCO3_LSB=0x00

ADC_DEC_CHAN_B_DDC0_NCO3_MSB=0x00

ADC_DEC_CHAN_B_DDC1_NCO4_LSB=0x00

ADC_DEC_CHAN_B_DDC1_NCO4_MSB=0x00

ADC_DEC_CHAN_B_DDC0_6DB_GAIN=0x01

ADC_DEC_CHAN_B_DDC1_6DB_GAIN=0x01

ADC_DEC_CHAN_B_WBF_6DB_GAIN=0x01 // USING WB DDC SO ADD 6DB GAIN

ADC_DEC_CHAN_B_NCO_SEL_PIN=0x00 // NCO SELECTED THROUGH SPI

ADC_DEC_CHAN_B_NCO_SEL=0x00 // NCO 1 SELECTED

ADC_DEC_CHAN_B_LMFC_RESET_MODE=0x00 // ALL DDCS AND NCOS RESET WITH EVERY LMFC

//ADC_DEC_CHAN_B_DDC_DET_LAT=0x50 // ENSURE DETERMINISTIC LATENCY FOR DEC BY 4, DEC BY 8

ADC_DEC_CHAN_B_DDC_DET_LAT=0x20 // ENSURE DETERMINISTIC LATENCY FOR DEC BY 16

Is there something that I am not setting correctly for decimate by 16? Or is there something I am setting in the incorrect order for decimate by 16? Does the fact that the PLL MODE has changed to 40X have any other impact on the clocking, etc. that I need to take into account?

Thank you.