Other Parts Discussed in Thread: LMK04828

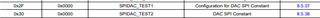

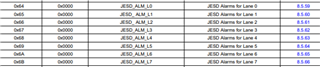

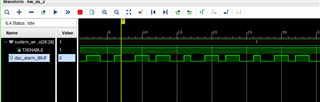

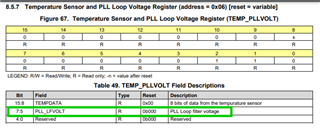

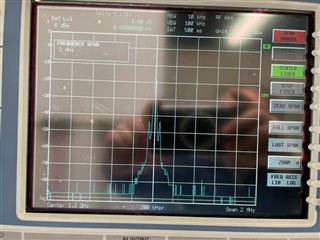

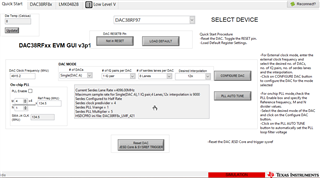

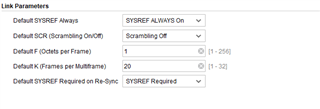

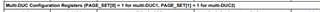

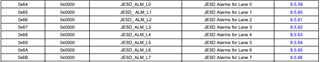

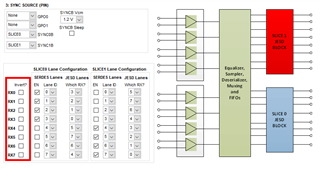

We are using this DAC38RF97 part in our radio project. Our design mainly based on the TI's reference design. We are having problem of NO OUTPUT. We have checked all voltages and they are normal and correct based on the data sheet. The SerDes inputs to the DAC is from Xilinx's Artix7 using Xilinx JESD204B IP and the lane speed is 4.8Gbps. We only use one of the DAC so we use only 4 pairs of lanes. The DAC PLL runs at 4.76GHz. And the lane data format is IQ paired.

Please advice what would be the possible issues and how to debug this problem.