Dear team,

our customer has a inquiry below

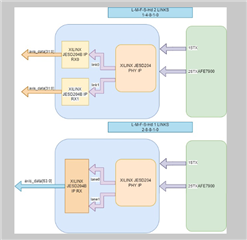

I want to communicate with AFE7900 in Xilinx FPGA. I need to design SERDERS Rate is 10 Gbps, and the output rates are 125 MSPS. I got some information about JESD204B configuration in device datasheet. AFE7900

Best regards,

William