Part Number: AFE7950EVM

Can AFE7950EVM run on Xilinx ZC706?

I want to develop program with LabVIEW and VIVADO. And I have get the TI-JESD204-IP but don't know how to start.

Can TI provide libraries and usages?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: AFE7950EVM

Can AFE7950EVM run on Xilinx ZC706?

I want to develop program with LabVIEW and VIVADO. And I have get the TI-JESD204-IP but don't know how to start.

Can TI provide libraries and usages?

Hi Chaoyang,

Do you have access to AFE79xx secure folder? We have an existing design using TI-JESD204-IP for AFE79xx and Xilinx ZCU102. You can use that as a reference.

The AFE7950EVM also works with ZC706. We might have already have an example design with ZC706 as well. I will check with the engineer working on this and see if we can provide this to you.

Regards,

Vijay

Hi Chaoyang,

The ZC706 + AFE79xx reference design can be found in the AFE79xx Secure folder. Please use this as a starting point for your design.

Regards,

David Chaparro

hi David,

I am chaoyang's colleague. What's the secure folder you mentioned? We acquired the AFE7950 data and it looks like

I did not see any file about zc706. Should I acquire another?

Hi LiehChun,

The secure folder was only recently updated to have the ZC706 reference design, so you may not have the project if you had previously downloaded the files. Please access the AFE79xx secure folder that you were granted access to and you can download the zc706 reference design. The folder can be accessed through this link,https://www.ti.com/securesoftware/, and will require you to sign in to your myTI account.

...

Regards,

David Chaparro

hi David,

Thanks your advice. I have downloaded and checked the ZC706 example. It can be implmented by Vivado.

I checked the design schematic file and found SPIB1 and SPIB2 linked to FT4232H. It looks like the SPI command came from USB to SPI through FT4232H. Is there any file that include the registers initialization or configuration?

The example is not a vivado project. I did not see the configuration through 7 series FPGA Transceivers Wizard. How do you configure the GTX line?

hi David,

Can TI provide how to confiure the GTX line? Because finally we do not use ZC706, we use our defined mother board with another FPGA and need to change the pin configuration.

Hi Chaoyang,

To fix this error the TX NCO needs to be updated to a value higher than 600MHz, as the AFE7950 does not support frequencies lower than 600Mhz Please update the NCO frequencies in the Latte script and give the script another try.

Regards,

David Chaparro

Hi David,

Thanks for your reply. The error is fixed.

I have some more questions.

1.What is available number of Number of Samples/Channel in ILA Analyser?

2.How to receive all 6 ADC channel data(4 RX/2 FB)?

What parameters should be modified?

Hi Chaoyang,

The number of samples should be set to 1024 as this is the number of samples captured in the ILAs in Vivado. I would recommend following the settings mentioned in the TI204c-Setup document in order to see all 4 Rx channels.

The reference design that is provided in the secure folder is not using the FB channels so it is not possible to capture the FB data. If the FB channels are needed them the Latte script and Vivado reference design will need to be updated. In Latte the FB channels would need to be enabled/setup properly and the Vivado project would need to be updated to match the new AFE settings.

Regards,

David Chaparro

Hi David

Would TI provide an updated reference design with FB channels enabled or provide more detail steps for updating the reference design?

Hi Chaoyang,

At this moment we do not have a reference design available with the FB channels enabled. To enabled the FB channels you will be required to update the Latte script to enable the FB channels and set the LMFS for both the Rx and Fb channels correctly. The example scripts, S1 and S2, provided with the Latte installation are a good reference for this. The FPGA project will have to be updated to match the new LMFS.

Regards,

David Chaparro

Hi Chaoyang,

In the FPGA project you will need to update the number of Rx lanes to match the number being used on the AFE and the transceiver IP should be updated to have those lanes enabled. Additionally the data unpacking for the Rx needs to be updated to match the new LMFS that is being used for the Rx and for the FB channels.

Regards,

David Chaparro

Hi David,

I am not sure what to do.

Do you mean

1.modify jesd_link_params.vh `define NUMBER_OF_RX_LANES 12

2.modify refdesign_rx.sv, add assign fb1_I_samples[i] = rx_lane_data[8][63-16*i -: ADC_RES];

assign fb1_Q_samples[i] = rx_lane_data[9][63-16*i -: ADC_RES];

assign fb2_I_samples[i] = rx_lane_data[10][63-16*i -: ADC_RES];

assign fb2_Q_samples[i] = rx_lane_data[11][63-16*i -: ADC_RES];

Do I need to modify the constraints.xdc or other file?

Hi Chaoyang,

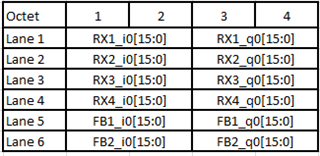

The AFE79xx device only has 8 STX lanes that can be used by both the Rx and Fb channels. This means that the AFE79xx configuration must be updated so that the 8 lanes are shared between the Rx and Fb channels. One way to do this is to update the Rx LMFS mode to 24410 and the Fb LMFS to 12410. This will configure the Rx and Fb channels to use a total of 6 lanes. Then you can update the jesd_link_params, refdesign_rx, and transceiver IP to use the 6 lanes. For the refdesign_rx file the data unpacking would need to be updated for the Rx and Fb because now that the LMFS is 24410 or 12410 the data format will now be:

The Latte script that is configured for the mode I mentioned is below.

############## Read me ##############

#In HSDC Pro DAC tab, Select AFE79xx_2x2TX_44210; Data Rate = 491.52M

#In HSDC Pro ADC tab, Select AFE79xx_2x2RX_24410; Data Rate = 245.76M ---> To capture 4 RX channels

#In HSDC Pro ADC tab, Select AFE79xx_1x2FB_44210; Data Rate = 491.52M ---> To capture 2 FB channels

sysParams=AFE.systemParams

sysParams.__init__();sysParams.chipVersion=chipVersion

setupParams.skipFpga = 1 # setup FPGA (TSW14J56) using HSDC Pro

############## Top Level ##############

sysParams.FRef = 491.52

sysParams.FadcRx = 2949.12

sysParams.FadcFb = 2949.12

sysParams.Fdac = 2949.12*4

sysParams.externalClockRx=False

sysParams.externalClockTx=False

############## Digital Chain ##############

##### RX #####

sysParams.ddcFactorRx = [12,12,12,12] #DDC decimation factor for RX A, B, C and D

sysParams.rxNco0 = [[5400,5400], #Band0, Band1 for RXA

[500,500], #Band0, Band1 for RXB

[2500,2500], #Band0, Band1 for RXC

[1800,1800]] #Band0, Band1 for RXD

##### FB #####

sysParams.ddcFactorFb = [12,12] #DDC decimation factor for FB 1 and 2

sysParams.fbNco0 = [500,1800] #Band0 for FB1 and FB2

##### TX #####

sysParams.ducFactorTx = [24,24,24,24] #DUC interpolation factor for TX A, B, C and D

sysParams.txNco0 = [[5400,5400], #Band0, Band1 for TXA

[500,500], #Band0, Band1 for TXB

[2600,2500], #Band0, Band1 for TXC

[1800,1800]] #Band0, Band1 for TXD

############## JESD ##############

##### ADC-JESD #####

sysParams.jesdSystemMode= [1,1]

#SystemMode 0: 2R1F-FDD ; rx1-rx2-fb -fb

#SystemMode 1: 1R1F-FDD ; rx -rx -fb -fb

#SystemMode 2: 2R-FDD ; rx1-rx1-rx2-rx2

#SystemMode 3: 1R ; rx -rx -rx -rx

#SystemMode 4: 1F ; fb -fb- fb -fb

#SystemMode 5: 1R1F-TDD ; rx/fb-rx/fb-rx/fb-rx/fb

sysParams.jesdTxProtocol= [0,0] # 0 - 8b/10b encoding; 2 - 64b/66b encoding

sysParams.LMFSHdRx = ["24410","24410","24410","24410"]

# The 2nd and 4th are valid only for jesdSystemMode values in (0,2).

# For other modes, select 4 converter modes for 1st and 3rd.

sysParams.LMFSHdFb = ["12410","12410"]

sysParams.rxJesdTxScr = [True,True,True,True]

sysParams.fbJesdTxScr = [True,True]

sysParams.rxJesdTxK = [32,32,32,32]

sysParams.fbJesdTxK = [32,32]

sysParams.jesdTxLaneMux = [0,1,2,3,4,5,6,7] # Enter which lanes you want in each location.

# For example, if you want to exchange the first two lines of each 2T,

# this should be [[1,0,2,3],[5,4,6,7]]

##### DAC-JESD #####

sysParams.jesdRxProtocol= [0,0]

sysParams.LMFSHdTx = ["44210","44210","44210","44210"]

sysParams.jesdRxLaneMux = [0,1,2,3,4,5,6,7] # Enter which lanes you want in each location.

# For example, if you want to exchange the first two lines of each 2R

# this should be [[1,0,2,3],[5,4,6,7]]

sysParams.jesdRxRbd = [4, 4]

sysParams.jesdRxScr = [True,True,True,True]

sysParams.jesdRxK = [32,32,32,32]

##### JESD Common #####

sysParams.jesdABLvdsSync= False

sysParams.jesdCDLvdsSync= False

sysParams.syncLoopBack = True #JESD Sync signal is connected to FPGA

############## GPIO ##############

sysParams.gpioMapping = {

'H8': 'ADC_SYNC0',

'H7': 'DAC_SYNC0',

'N8': 'ADC_SYNC2',

'N7': 'ADC_SYNC3',

'H9': 'ADC_SYNC1',

'G9': 'DAC_SYNC1',

'N9': 'DAC_SYNC2',

'P9': 'DAC_SYNC3',

'P14': 'GLOBAL_PDN',

'K14': 'FBABTDD',

'R6': 'FBCDTDD',

'H15': ['TXATDD','TXBTDD'],

'V5': ['TXCTDD','TXDTDD'],

'E7': ['RXATDD','RXBTDD'],

'R15': ['RXCTDD','RXDTDD']}

############## LMK Params ##############

lmkParams.pllEn = True

lmkParams.inputClk = 983.04 # Valid only when lmkParams.pllEn = False

lmkParams.lmkFrefClk = True

setupParams.fpgaRefClk = 122.88 # Should be equal to LaneRate/40 for TSW14J56

############## Logging ##############

logDumpInst.setFileName(ASTERIX_DIR+DEVICES_DIR+r"\Afe79xxPg1.txt")

logDumpInst.logFormat=0x0 #Modify to 0x1 to save register scequence to log file. Script takes more time to execute.

logDumpInst.rewriteFile=1

logDumpInst.rewriteFileFormat4=1

device.optimizeWrites=0

device.rawWriteLogEn=1

device.delay_time = 0

#-------------------------------------------------------------------------------------------------#

setupParams.skipLmk = False

AFE.initializeConfig()

lmkParams.sysrefFreq = AFE.systemStatus.sysrefFreq

lmkParams.lmkPulseSysrefMode = False

AFE.LMK.lmkConfig()

Regards,

David Chaparro

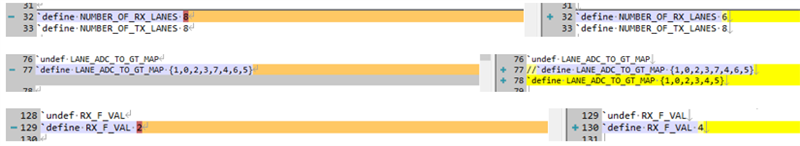

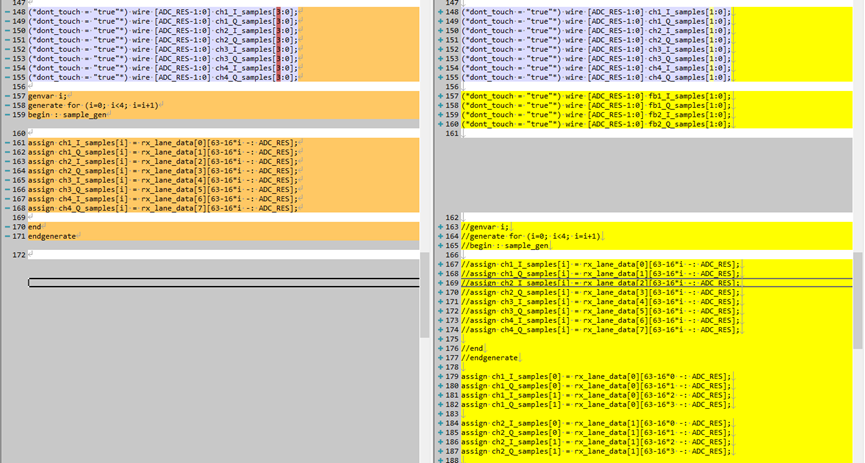

Hi David,

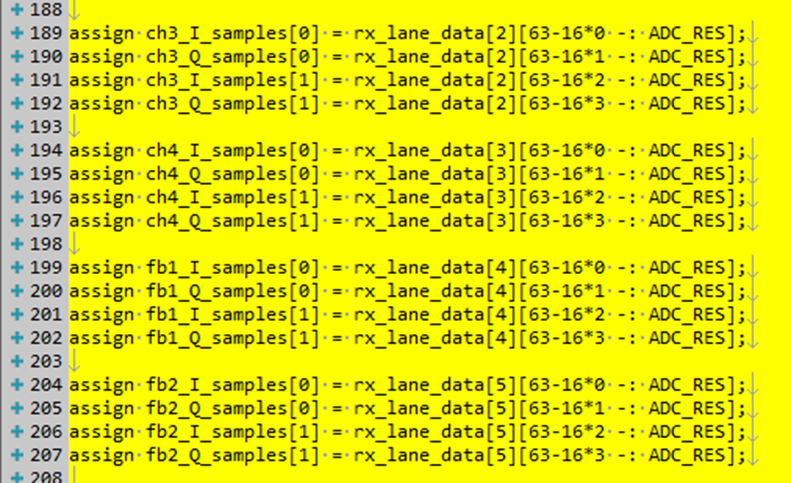

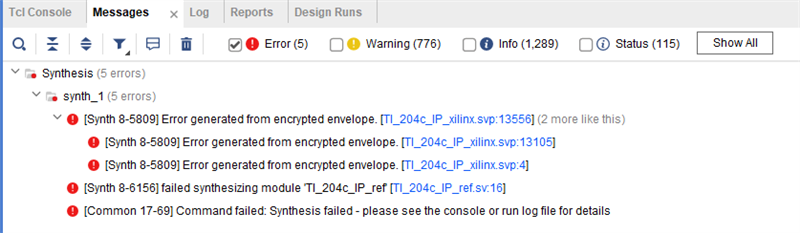

I modify the code as following pic

jesd_link_params.vh:

TI_204c_IP_ref.sv:

refdesign_rx.sv:

Then, I get error in vivado.

What else need to be modified?

Hi Chaoyang,

Our team has just came back from the holidays. We are working on checking your modifications now.

Regards,

David Chaparro

Hi Chaoyang,

I have created a reference design for the ZC706 that has both the Rx and Fb enabled. Please access the reference design through the AFE79xx secure folder. The reference design is named AFE79xx_ZC706_4T4R2F.

Regards,

David Chaparro

Hi David,

I didn't get the Fb1/2 on ila waveform and the max adc value of rxa\b\c\d are different.

I set all rx/fb NCO as 2000 and connect the same 2.1GHz signal to all ch.

What else need to be modified?

rxa

rxb

rxc

rxd

Hi Chaoyang,

The reason that there is no data on the FB channels is most likely because they are in standby mode. Please update the command below in the ConfigAfe script and you should be able to see both Rx and Fb channels.