Hi TI,

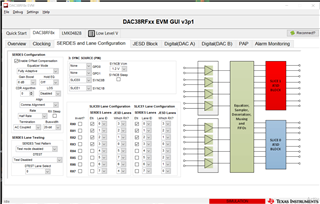

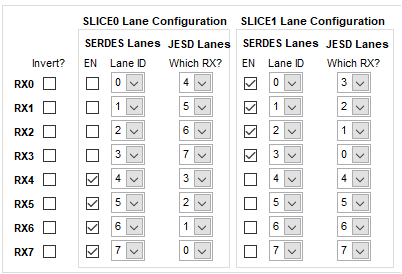

I am using dac38rf80 in 88210(2 TX ) mode with x16 interpolation on our custom PCB.

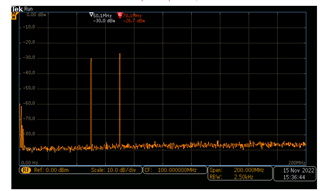

we are sending same data for both the DAC, but first TX is giving correct output of single peak, but second TX is giving 2 peaks. but configuration happening to both the DAC is same

dac configuration :-

input_clk :- 3200 MHZ(differential)

DUAL DAC

2 IQ pairs per dac

4 serdes lanes per dac

interpolation x16

serdes rate 4.0gbps

sysref frequency 6.25MHZ

k = 30

DAC inputs :-

A1_I0 -> 10mhz I data

A1_Q0 -> 10mhz Q data

A1_I1 -> 10 mhz I data

A1_Q1 -> 10mhz Q data

B1_I0 -> 10mhz I data

B1_Q0 -> 10mhz Q data

B1_I1 -> 10 mhz I data

B1_Q1 -> 10mhz Q data

DAC NCO -> 60MHZ

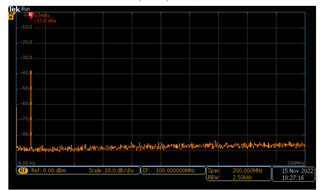

DAC -A output

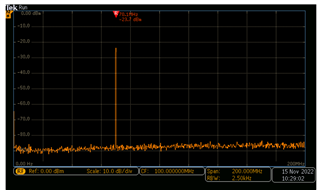

DAC B outputs:-

Any help would be highly appreciated.

x09 x0000

x01 x1880

x01 x1880

x00 x5803

x00 x5803

x09 x0004

x31 x1000

x32 x0308

x33 x4018

x31 x1000

x31 x1000

x0b x0022

x3b x0002

x3b x1802

x33 x4018

x3c x8229

x3c x8229

x3c x8229

x3c x8229

x3c x8229

x3c x8229

x31 x1000

x3b x1801

x32 x0308

x0c xa002

x09 x0001

x25 x3700

x25 x3700

x09 x0002

x25 x3300

x25 x3700

x09 x0004

x0b x0022

x0c xa002

x0c xa002

x24 x1000

x33 x4018

x09 x0001

x4a x0103

x5f x3123

x4a x0303

x5f x3223

x4a x0703

x5f x3213

x4a x0f03

x5f x3210

x4a x0f03

x60 x5567

x4a x0f03

x60 x5767

x4a x0f03

x60 x5767

x4a x0f03

x60 x5764

x09 x0004

x3e x0929

x09 x0002

x4a x0003

x5f x5123

x4a x0003

x5f x5723

x4a x0003

x5f x5763

x4a x0003

x5f x5764

x4a x1003

x60 x3567

x4a x3003

x60 x3267

x4a x7003

x60 x3217

x4a xf003

x60 x3210

x09 x0001

x4e x0f0f

x4d x0100

x4e x0f0f

x4d x0300

x4c x1d03

x4c x1d03

x4b x1301

x4a x0f03

x09 x0002

x4e x0f0f

x4d x0100

x4e x0f0f

x4d x0300

x4c x1d03

x4c x1d03

x4b x1301

x4a xf003

x09 x0001

x0a x08b0

x0a x88b0

x09 x0002

x0a x82b0

x0a x88b0

x09 x0001

x4c x1d03

x5c x0002

x4f x1c41

x0d x0300

x4f x1c61

x4f x1c60

x51 x007f

x51 x003f

x51 x001f

x51 x000f

x09 x0000

x00 x5802

x09 x0002

x4c x1d03

x5c x0003

x4f x1c41

x0d x0300

x4f x1c61

x4f x1c60

x51 x007f

x51 x003f

x51 x001f

x51 x000f

x09 x0000

x00 x5800

x09 x0001

x0a x8830

x0a x8810

x0a x8800

x0d x8301

x0c x2602

x0c x2702

x27 x8144

x27 x8844

x0c x2722

x0c x2732

x27 x8884

x27 x8888

x28 x0300

x28 x0330

x09 x0002

x28 x0300

x28 x0330

x09 x0001

x1e xcccd

x1f xcccc

x20 x04cc

x21 x3333

x22 x3333

x23 x0733

x1c x0000

x1d x0000

x28 x0332

x28 x0330

x09 x0002

x28 x0332

x28 x0330

x09 x0001

x19 x0001

x09 x0002

x0a x8830

x0a x8810

x0a x8800

x0d x8301

x0c x2602

x0c x2702

x27 x8144

x27 x8844

x0c x2722

x0c x2732

x27 x8884

x27 x8888

x1e xcccd

x1f xcccc

x20 x04cc

x21 x3333

x22 x3333

x23 x0733

x1c x0000

x1d x0000

x09 x0001

x28 x0332

x28 x0330

x09 x0002

x28 x0332

x28 x0330

x19 x0001