Part Number: AFE7920EVM

Hi Team,

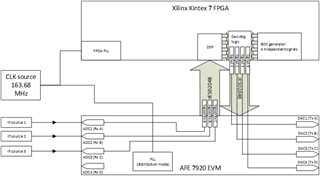

We've been recently trying to connect the AFE7920EVM to a Kintex-7-like FPGA (XC7K410T) in a way indicated by the following schematic:

For the programming of the AFE EVM the attached script is being used (thanks to the input of TIs David Chaparro) and it is capable of being compiled on the AFE side without any errors.

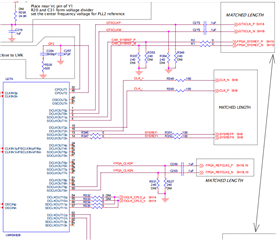

However, the connected FPGA seems to be having some issues, as it does not see the proper clocks coming from the AFE side. Due to this, during the debugging we tried manually to probe the LMK outputs on the AFE side just to see if it is outputting the proper clock (LMK is supposed to be in distribution mode, as its input is 163.68 MHz external reference clock, and all the system relevant frequencies are its derivatives). Based on the schematics of the LMK (see below) GTXCLK inputs are expected, as well as FPGA_SYSREF and FPGA_REFCLK2 to be 163.68 MHz (in our first interpretation).

However, after probing it with a scope, a signal with frequency of 5.115 MHz is detected, where 5.115 is a factor of 163.68 (5.115x32=163.68). After a bit of digging through the Latte code and workspace, I managed to find that the same number (5.115) can be seen in the following variables:

lmkParams.sysrefFreq and AFE.systemStatus.sysrefFreq

and it seems that no matter what I do, I cannot overwrite them so that measured output has frequency any different than 5.115 MHz.

Can the TI staff help me resolve this issue of understanding where this 5.11 number comes from and if can and should be modified so LMK can provide 163.68 MHz at its output to the FPGA?

Kind regards,

Željko

########## General settings: ##########

# VLBI Tx frequency plan details:

custom_clk = 2

ncoFreqModes = ["1KHz", "FCW"]

Fnco_tx1 = 2245.0

Fnco_rx1 = 500.0

if custom_clk == 0:

f0 = 122.88

Nrx = 24

Nddc = 12

Ntx = 3

NFRef = 4

NfpgaRefClk = 2

NinputClk = 12

LMFSHdRx = ['24410', '24410', '24410', '24410']

LMFSHdFb = ['24410', '24410']

LMFSHdTx = ['24410', '24410', '24410', '24410']

syncLoopBack = False

elif custom_clk == 2:

f0 = 163.68

Nrx = 12

Nddc = 6

Ntx = 3

NFRef = 1

NfpgaRefClk = 1

NinputClk = 1

LMFSHdRx = ['22210', '22210', '22210', '22210']#['44210', '44210', '44210', '44210']

LMFSHdFb = ['22210', '22210']

LMFSHdTx = ['22210', '22210', '22210', '22210']#['44210', '44210', '44210', '44210']

syncLoopBack = False#True#

Nduc = Nddc*Ntx

# AFE general settings

AFE.systemStatus.loadTrims = 1

setupParams.skipFpga = 1

setupParams.fpgaRefClk = f0*NfpgaRefClk

sysParams = AFE.systemParams

sysParams.FRef = f0*NFRef

########## Analog settings: AFE 79XX EVM ##########

# General system settings

sysParams.RRFMode = 0

sysParams.modeTdd = 0

sysParams.adcSelect0 = [0, 1, 2]

sysParams.adcSelect1 = [0, 1, 2]

sysParams.useSpiSysref = 0

sysParams.sysrefTermination = 0

sysParams.ncoFreqMode = ncoFreqModes[custom_clk != 0]

sysParams.spiMode = 1

# ADC settings

sysParams.FadcRx = f0*Nrx

sysParams.rxEnable = [1, 1, 1, 1]

sysParams.externalClockRx = 0

sysParams.halfRateModeRx = [0, 0]

sysParams.ddcFactorRx = [Nddc, Nddc, Nddc, Nddc]

sysParams.numBandsRx = [0, 0, 0, 0]

sysParams.numRxNCO = 1

sysParams.ncoRxMode = [0, 0]

sysParams.broadcastRxNcoSel = 0

sysParams.rxNco0 = [ [Fnco_rx1, Fnco_rx1],

[870.0, 870.0],

[637.5, 637.5],

[637.5, 637.5]]

sysParams.rxNco1 = [ [Fnco_rx1, Fnco_rx1],

[870.0, 870.0],

[637.5, 637.5],

[637.5, 637.5]]

# FB settings

sysParams.FadcFb = sysParams.FadcRx

sysParams.fbEnable = [0, 0]

sysParams.halfRateModeFb = [0, 0]

sysParams.ddcFactorFb = [Nddc, Nddc]

sysParams.numBandsFb = [0, 0]

sysParams.numFbNCO = 1

sysParams.ncoFbMode = 0

sysParams.fbNco0 = [1000, 1000]

sysParams.fbNco1 = [1000, 1000]

sysParams.fbNco2 = [1000, 1000]

sysParams.fbNco3 = [1000, 1000]

# DAC settings

# DAC sampling rate must fall into one of the following frequency ranges (due to pll restrictions): [7.2 GHz, 7.68 GHz] or [8.8 GHz, 9.1 GHz] or [9.7 GHz, 10.24 GHz] or [11.6 GHz, 12.08 GHz]

sysParams.Fdac = sysParams.FadcRx*Ntx

sysParams.txEnable = [1, 1, 1, 1]

sysParams.externalClockTx = 0

sysParams.halfRateModeTx = [0, 0]

sysParams.ducFactorTx = [Nduc, Nduc, Nduc, Nduc]

sysParams.numBandsTx = [0, 0, 0, 0]

sysParams.numTxNCO = 1

sysParams.combineDucMode = [0, 0]

sysParams.enableDacInterleavedMode = 0

sysParams.ncoTxMode = [0, 0]

sysParams.broadcastTxNcoSel = 0

sysParams.txNco0 = [ [Fnco_tx1, Fnco_tx1],

[5020.0, 5020.0],

[8212.5, 8212.5],

[6812.5, 6812.5]]

sysParams.txNco1 = [ [Fnco_tx1, Fnco_tx1],

[5020.0, 5020.0],

[8212.5, 8212.5],

[6812.5, 6812.5]]

########## Clock distribution mode setting ##########

setupParams.skipLmk = 0

lmkParams.pllEn = (custom_clk == 0)

lmkParams.inputClk = f0*NinputClk

lmkParams.sysrefFreq = lmkParams.inputClk#f0*Nrx/1024

lmkParams.lmkFrefClk = 1

lmkParams.lmkPulseSysrefMode = 0

#AFE.systemStatus.sysrefFreq = lmkParams.inputClk

#AFE.LMK.lmkConfig()

########## JESD204 settings AFE 79XX EVM ##########

sysParams.topLevelSystemMode = 'StaticTDDMode'

sysParams.jesdSystemMode = [3, 3]

sysParams.serdesFirmware = 1

sysParams.jesdABLvdsSync = 1

sysParams.jesdCDLvdsSync = 1

sysParams.syncLoopBack = syncLoopBack

sysParams.jesdLoopbackEn = 1

sysParams.setIlaParams = 1

sysParams.jesdTxIlaM = [8, 8, 2, 8, 8, 2]

sysParams.jesdTxIlaLid = [0, 1, 2, 3, 4, 5, 6, 7]

sysParams.jesdTxIlaL = [4, 4, 2, 4, 4, 2]

sysParams.LMFSHdRx = LMFSHdRx

sysParams.jesdRxProtocol = [0, 0]

sysParams.jesdRxLaneMux = [0, 1, 2, 3, 4, 5, 6, 7]

sysParams.jesdRxRbd = [4, 4]

sysParams.rxJesdTxScr = [1, 1, 1, 1]

sysParams.rxJesdTxK = [16, 16, 16, 16]

sysParams.rxJesdTxSyncMux = [0, 0, 0, 0]

sysParams.rxDataMux = [0, 1, 2, 3, 4, 5, 6, 7]

sysParams.serdesRxLanePolarity = [0, 0, 0, 0, 0, 0, 0, 0]

sysParams.adcDataMuxEn = 0

sysParams.LMFSHdFb = LMFSHdFb

sysParams.fbJesdTxScr = [1, 1]

sysParams.fbJesdTxK = [16, 16]

sysParams.fbJesdTxSyncMux = [0, 0]

sysParams.fbDataMux = [0, 1]

sysParams.LMFSHdTx = LMFSHdTx

sysParams.jesdTxProtocol = [0, 0]

sysParams.jesdTxLaneMux = [0, 1, 2, 3, 4, 5, 6, 7]

#sysParams.jesdTxRbd = [4, 4]

sysParams.jesdRxScr = [1, 1, 1, 1]

sysParams.jesdRxK = [16, 16, 16, 16]

sysParams.jesdRxSyncMux = [0, 0, 0, 0]

sysParams.txDataMux = [0, 1, 2, 3, 4, 5, 6, 7]

sysParams.serdesTxLanePolarity = [0, 0, 0, 0, 0, 0, 0, 0]

#sysParams.dacDataMuxEn = 0

#sysParams.serdesTxPreCursor = [6, 6, 6, 6, 6, 6, 6, 6]

#sysParams.serdesTxPostCursor = [0, 0, 0, 0, 0, 0, 0, 0]

#sysParams.serdesTxMainCursor = [3, 0, 0, 0, 0, 0, 0, 3]

########## Dummy txt ##########

sysParams.gpioMapping={ 'H8': 'ADC_SYNC0',

'H7': 'ADC_SYNC1',

'N8': 'ADC_SYNC2',

'N7': 'ADC_SYNC3',

'H9': 'DAC_SYNC0',

'G9': 'DAC_SYNC1',

'N9': 'DAC_SYNC2',

'P9': 'DAC_SYNC3',

'P14': 'GLOBAL_PDN',

'K14': 'FBABTDD',

'R6': 'FBCDTDD',

'H15': ['TXATDD','TXBTDD'],

'V5': ['TXCTDD','TXDTDD'],

'E7': ['RXATDD','RXBTDD'],

'R15': ['RXCTDD','RXDTDD']}

lmk.rawWriteLogEn = 1

lmk.logEn = 1

logDumpInst.setFileName(ASTERIX_DIR+DEVICES_DIR+r"\Afe79xxPg1.txt")

logDumpInst.logFormat = 0x01

logDumpInst.rewriteFile = 1

logDumpInst.rewriteFileFormat4 = 1

device.optimizeWrites = 0

device.rawWriteLogEn = 1

device.delay_time = 0

AFE.deviceBringup()

AFE.TOP.overrideTdd(15,3,15)

AFE.saveCAfeParamsFile()