Other Parts Discussed in Thread: AFE7900, AFE7950, AFE7900EVM,

Hello,

We are using the eval boards of both AFE7900 and AFE7950 (EVMs) connected to a ZCU102.

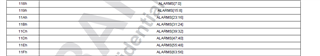

Background: We have a design that works on the AFE7900EVM (specifically channels C and D are used). The register values were extracted from Latte's log (for AFE7900) and written to the AFE (again, working setup)

Now we would like to test the same working design on the AFE7950EVM. We replaced the 7900EVM with the 7950EVM. However we are unable to see any output from the Tx ports. The Rx ports are working (as captured through ILA). A digital loopback (Rx connected to Tx inside the FPGA) also doesn't give out any signal.(the signals can be seen on ILA). It seems that there is some setting in the AFE7950 which has to be configured differently.

We confirm that the AFE7950EVM is a working board (as we tested with a basic design and configured it directly from Latte).

qpll lock and rxlmfc_buffer_delay give the right values (on 7950EVM)

Thank you for your help in advance,