HI,

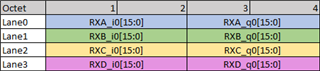

I need to check JESD data format for ADC/DAC of AFE. Both LMFSHdRx and LMFSHdTx are '24410' - Four lane for 4 DAC/ADC. one I/Q set per lane

I am using Xilinx JESD IP and on its datasheet there is a note saying "tx_tdata transfer JESD204B transport layer, not raw converter samples".

I sent 16bit signed integer I/Q data and no control bit to JESD IP for DAC, but did not see RF output I expected.

1> Let me know how to map I/Q data to/from transport layer for DAC/ADC.

2> Xilinx IP transmitted least significant byte first. I connect I[15:0] data to low word[15:0] and Q[15:0] data to high word[31:16]. Thus I[7:0] will be transmitted first, then I[15:8], Q[7:0] and Q[15:8] will be sent last. Let me know the right sequence of I/Q datra.

3> Actually I am very confused about I/Q data format. In the refdesign_tx.sv file, reference design ZCU102_AFE79xx_8b10b_10Gbps.zip, 16bit signed integer-tone is generated and sent to TI_IP. Thus I thought the data to/from FPGA would be 16-bit signed integer. However there is a Table 8-3 floating point format on afe7950 datasheet. Do the register field FLAOT_PT_MODE and FLOAT_PT_FORMAT mean the register 0x6d4 and 0x6d5 in RX Top Register Map? When register 0x6d4 is not written after power on so its value is 0 as default, what is the format of data to be sent to FPGA?

Regards,

YS