Hi everyone,

I want to send data to the DAC using FPGA,In my understanding, I need a reset signal to the FPGA that my link has been set up to allow him to send data.

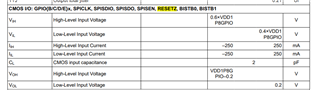

I found resetZ in the datasheet,But it seems to be an input signal?And the reset_FPGA interface with FMC doesn't seem to work.

I attach the related pictures below.I hope I can get some answers