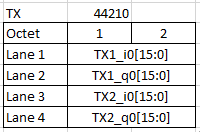

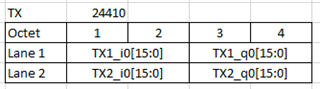

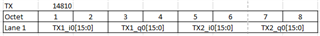

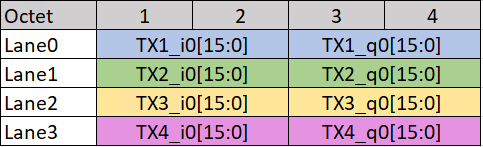

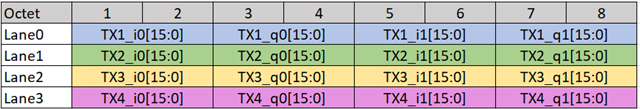

Do you have mapping table with AFE7900's LMFS vs JESD204B and its LINE DATA WIDTH(32/64BIT)?

Currently using TI-204C IP on the FPGA side, but I don't know what to do Mapping (DAC/ADC) IQ data.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.