Other Parts Discussed in Thread: LMK04828,

Hello,

I am developing an mmWave application using two AFE7950 devices.

My board consists of an MPSoC (XCZU11EG@AMD) + LMK04828 + AFE7950(x2) configuration.

1. Is the AFE7950 device suitable for my mmWave application, including beamforming?

2. Is there a feature in the AFE7950 that allows alignment of NCO phase between internal channels?

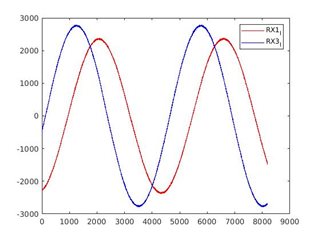

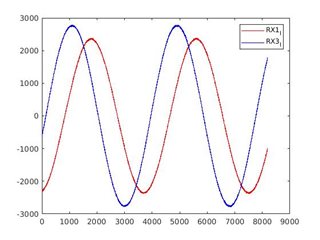

There seems to be a phase difference between TX/RX channels.

When powering on/off, the phase difference remains constant (e.g., Ch2-Ch1: 55°).

This appears to be due to the internal NCO phase difference in the AFE7950.

Is there a feature in the AFE7950 that allows alignment of NCO phase between internal channels?

Alternatively, should I correct this using the NCOx_PHASE_OFFSET register?

Thank you!

Regards,

Park.