Other Parts Discussed in Thread: AFE7769D, AFE7769

Hi Ti Team,

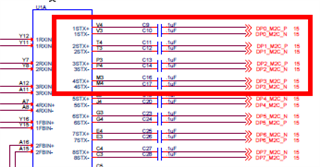

I saw serdes lanes swap on AFE7769DEVM, was the swapped set in the AFE7769D device by CPLD?

Let say, if i am designing a FPGA FMC mating connector to AFE7769DEVM, i just want to double confirm that i do not need the serdes lanes swapping on my side, was that true?

Thanks,

Best regards,

Alder