Hi

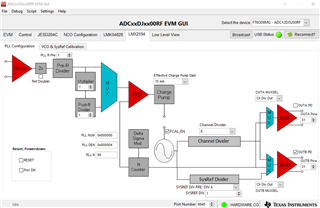

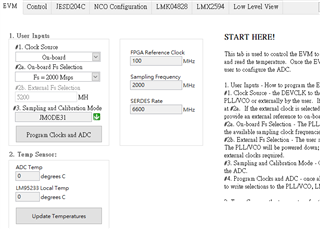

I used ADC12DJ5200RF EVM GUI . and it does not connect with FPGA EVM.

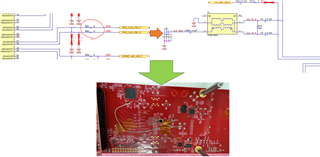

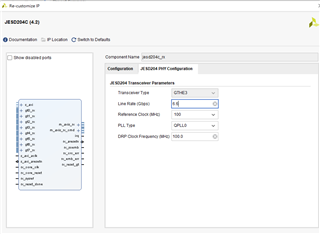

FOLLOWING PIC1 JMODE 1 SETTING , jesd204C's block SERDES PLL LOCKED light on .

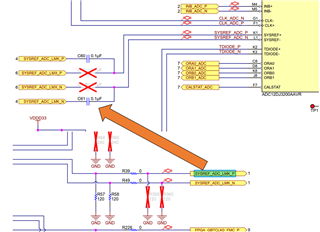

but PIC2 JMODE 2 SERDES PLL LOCKED doesn't light on .

what is the different?

and what is the meaning of SERDES PLL LOCKED ?

PIC1 :

PIC2 :