Part Number: TRF1208-AFE7950EVM

Hi Team

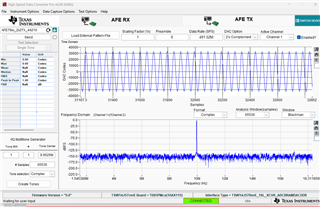

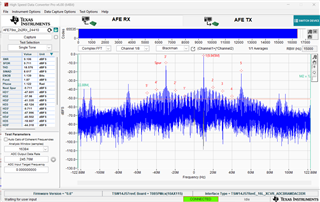

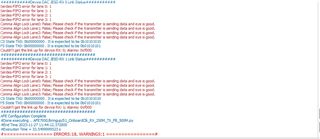

We are trying to interface TRF1208-AFE7950EVM with TSW14J57EVM and followed a bring-up presentation to interface both these devices to test the basic signal generation and capture capabilities of AFE7950. However, we are running into errors even after several retries. The error screenshot on the latte is as follows:

The process we have followed is mentioned in the presentation by the name: "AFE7950+TSW14J57" available in "AFE79xxEVM_TSW14J57_BringupGuides" folder in the secure folder.

Can you please help us resolve this error and share the reason for this error?

The log is as follows:

#Executing .. AFE7950/bringup/setup.py

#Start Time 2023-11-27 11:38:18.747000

AFE79xxLibraryPG1p0

spi - USB Instrument created.

resetDevice

Purge

Kintex RegProgrammer - USB Instrument created.

Kintex RegProgrammer - USB Instrument created.

Kintex RegProgrammer - USB Instrument created.

#Done executing .. AFE7950/bringup/setup.py

#End Time 2023-11-27 11:38:25.627000

#Execution Time = 6.88000011444 s

#================ ERRORS:0, WARNINGS:0 ================#

#======

#Executing .. AFE7950/bringup/devInit.py

#Start Time 2023-11-27 11:39:13.658000

Power Card - USB Instrument created.

Reset the FPGA and try again.

Device with name CPLD already exist. Please change the name to get new device.

Loaded Libraries

Refreshed GUI

#Done executing .. AFE7950/bringup/devInit.py

#End Time 2023-11-27 11:39:19.540000

#Execution Time = 5.88199996948 s

#================ ERRORS:1, WARNINGS:1 ================#

#======

#Executing .. AFE7950/bringup/S1_OnboardClk_RX_250M_TX_FB_500M.py

#Start Time 2023-11-27 11:43:38.822000

The External Sysref Frequency should be an integer factor of: 3.84MHz

2T2R1F Number: 0

Valid Configuration: True

laneRateRx: 9830.4

laneRateFb: 9830.4

laneRateTx: 9830.4

2T2R1F Number: 1

Valid Configuration: True

laneRateRx: 9830.4

laneRateFb: 9830.4

laneRateTx: 9830.4

LMK Clock Divider - Device registers reset.

LMK Clock Divider - Device registers reset.

REFCLOCK is used from LMK source, ensure board connections are ok to do the same

LMK and FPGA Configured.

DONOT_OPEN_Atharv_FULL - Device registers reset.

chipType: 0xa

chipId: 0x78

chipVersion: 0x11

AFE Reset Done

Fuse farm load autoload done successful

No autload error

Fuse farm load autoload done successful

No autload error

//Firmware Version = 11000

//PG Version = 1

//Release Date [dd/mm/yy] = 10/7/19

patchSize=11697

//Patch Version = 165

//PG Version = 0

//Release Date [dd/mm/yy] = 27/11/21

AFE MCU Wake up done and patch loaded.

PLL Locked

AFE PLL Configured.

AFE SerDes Configured.

AFE Digital Chains configured.

AFE TX Analog configured.

AFE RX Analog configured.

AFE FB Analog configured.

AFE JESD configured.

AFE AGC configured.

AFE GPIO configured.

Sysref Read as expected

###########Device DAC JESD-RX 0 Link Status###########

Serdes-FIFO error for lane 0: 1

Serdes-FIFO error for lane 1: 1

Serdes-FIFO error for lane 2: 1

Serdes-FIFO error for lane 3: 1

Comma Align Lock Lane0: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane2: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane3: False; Please check if the transmitter is sending data and eye is good.

CS State TX0: 0b00000000 . It is expected to be 0b10101010

FS State TX0: 0b00000000 . It is expected to be 0b01010101

Couldn't get the link up for device RX: 0; Alarms: 0xf000

###################################

###########Device DAC JESD-RX 1 Link Status###########

Serdes-FIFO error for lane 0: 1

Serdes-FIFO error for lane 1: 1

Serdes-FIFO error for lane 2: 1

Serdes-FIFO error for lane 3: 1

Comma Align Lock Lane0: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane2: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane3: False; Please check if the transmitter is sending data and eye is good.

CS State TX0: 0b00000000 . It is expected to be 0b10101010

FS State TX0: 0b00000000 . It is expected to be 0b01010101

Couldn't get the link up for device RX: 1; Alarms: 0xf000

###################################

AFE Configuration Complete

#Done executing .. AFE7950/bringup/S1_OnboardClk_RX_250M_TX_FB_500M.py

#End Time 2023-11-27 11:44:12.372000

#Execution Time = 33.5499999523 s

#================ ERRORS:18, WARNINGS:1 ================#

SPIA has Not got control of PLL pages

###########Device DAC JESD-RX 0 Link Status###########

Comma Align Lock Lane0: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane2: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane3: False; Please check if the transmitter is sending data and eye is good.

CS State TX0: 0b00000000 . It is expected to be 0b10101010

FS State TX0: 0b00000000 . It is expected to be 0b01010101

Couldn't get the link up for device RX: 0; Alarms: 0x0

###################################

###########Device DAC JESD-RX 1 Link Status###########

Comma Align Lock Lane0: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane2: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane3: False; Please check if the transmitter is sending data and eye is good.

CS State TX0: 0b00000000 . It is expected to be 0b10101010

FS State TX0: 0b00000000 . It is expected to be 0b01010101

Couldn't get the link up for device RX: 1; Alarms: 0x0

###################################

#======

SPIA has Not got control of PLL pages

###########Device DAC JESD-RX 0 Link Status###########

Comma Align Lock Lane0: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane2: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane3: False; Please check if the transmitter is sending data and eye is good.

CS State TX0: 0b00000000 . It is expected to be 0b10101010

FS State TX0: 0b00000000 . It is expected to be 0b01010101

Couldn't get the link up for device RX: 0; Alarms: 0x0

###################################

###########Device DAC JESD-RX 1 Link Status###########

Comma Align Lock Lane0: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane1: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane2: False; Please check if the transmitter is sending data and eye is good.

Comma Align Lock Lane3: False; Please check if the transmitter is sending data and eye is good.

CS State TX0: 0b00000000 . It is expected to be 0b10101010

FS State TX0: 0b00000000 . It is expected to be 0b01010101

Couldn't get the link up for device RX: 1; Alarms: 0x0

###################################

#======

has context menu

Thanks and Regards

Vinit Bansal

+91-9632438652