Hello Ti,

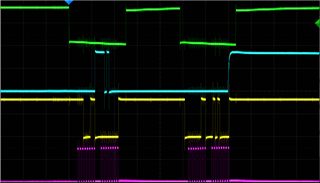

I am running the AFE7071 in 4 pin SPI mode by enabling bits 6 (sif_4pin) and 7 (alarm_or_sdo_ena) in register CONFIG3 (INTERFACE SELECTION). SDENB is set low when communicating to the AFE7071, in much the same way Chip Select works in SPI. When the SDENB signal goes high, it appears that the SDO pin 34 does not automatically revert to HighZ mode, rather it remains low. It appears that the only way to get ALARM_SDO to return to HighZ mode when register readout is done is to clear bit 7 (alarm_or_sdo_ena) in register CONFIG3 (INTERFACE SELECTION) by writing to that register again. When running in SPI mode, shouldn't the SDO pin return to HighZ when chip select is high?

Thank you