Other Parts Discussed in Thread: AFE7900EVM, LMK05318, LMK5B12204,

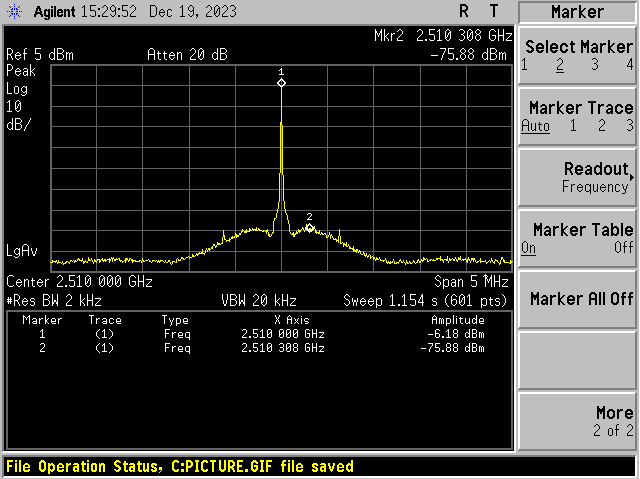

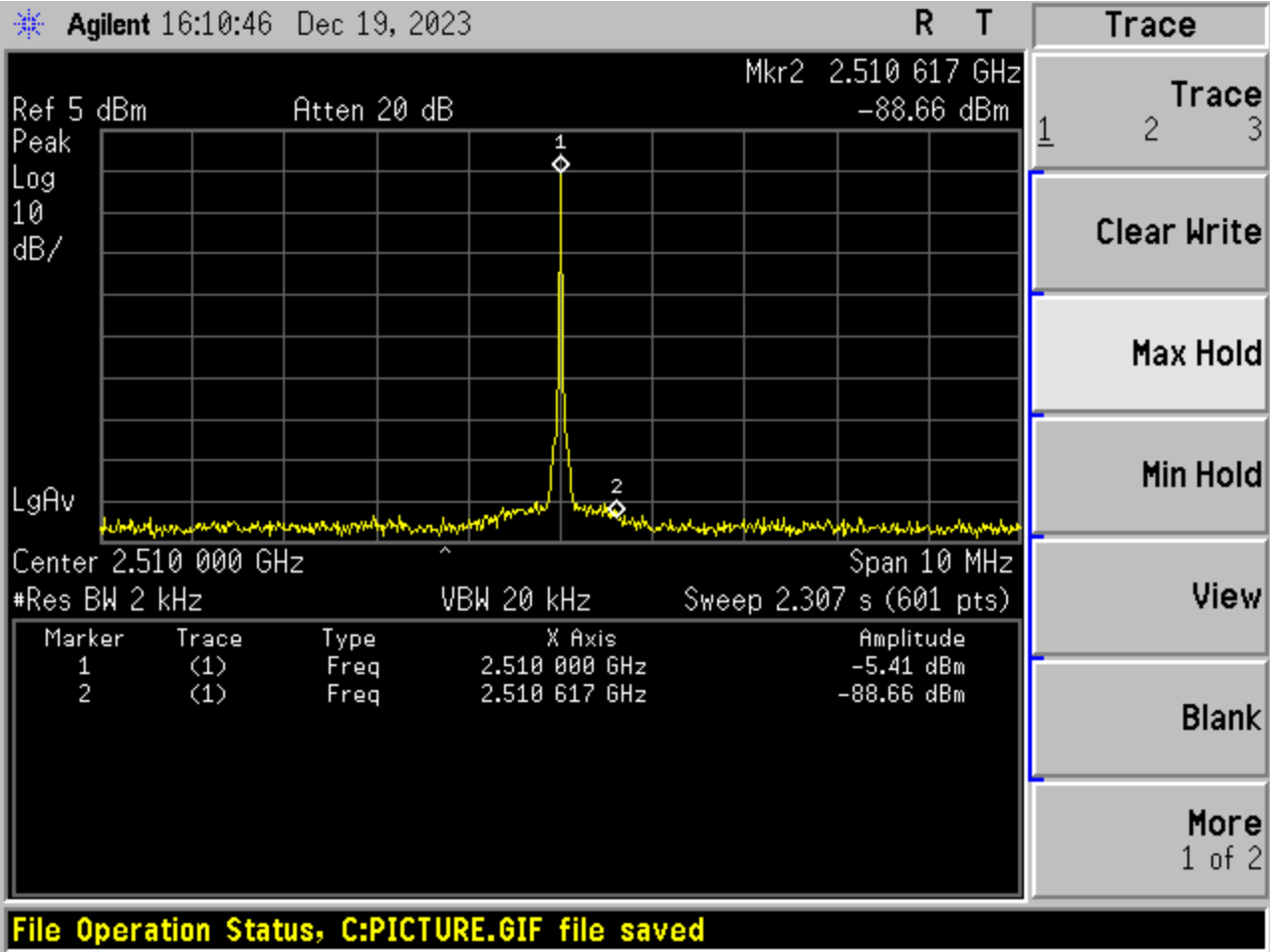

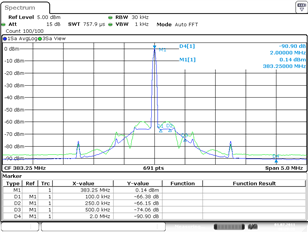

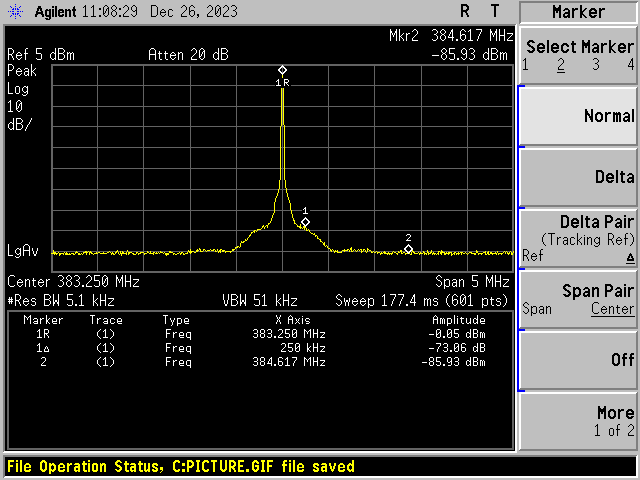

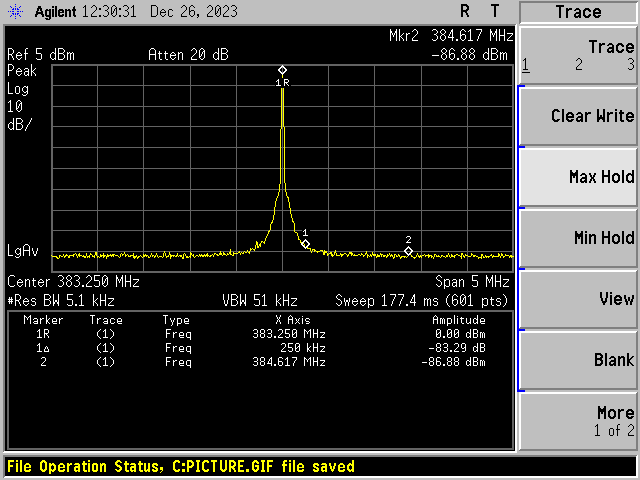

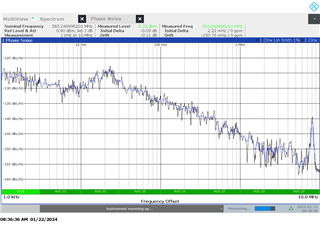

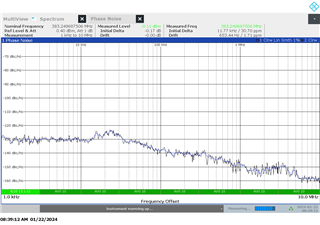

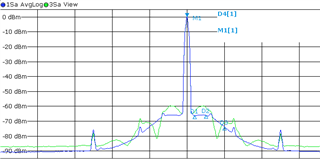

We are struggling with an unexpected noise shape around CW signals. It only appear if we use the same trx to sample the signal, process it an use the same trx to send it out. It happens with the loopback in the TRX and also happens if the loopback is done in the FPGA. Only the shape of the noise shoulder changes. If we acquire the signal or using synthetic signals to send out, we don't see such noise shoulders. Below you see an example

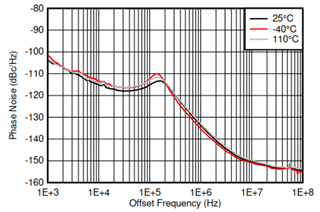

This noise shaping has often to do with dithering. So we played with dither register mentioned in the "AFE79xx Programming User Guide".

The bit TX_CLK_DITHERED_MODE_EN in register A0h in the JESD SubChip Register Map had an effect. If we read it back, it's set to 0x03 which means the clock is disabled and dithering is enabled. Writing a 0x03 again to this register removes the shoulders. That's weird. Writing a 1, 2 or 3 sometimes change something, generate spurs, reduces noise, destroys the signal completely or work perfect and smoothly. So I don't thinks it's a good idea to manually write to this register.

Can you explain what to do instead?