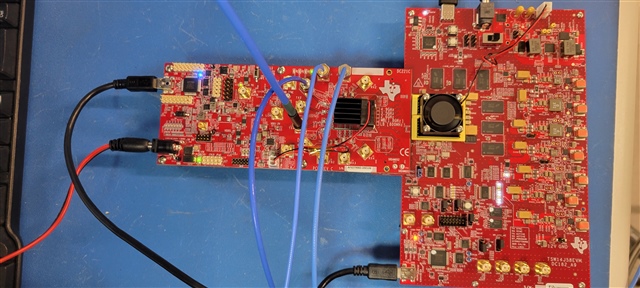

Other Parts Discussed in Thread: TSW14J58EVM, AFE7769D

Currently I am struggling on the set up.

Here I have several questions.

Could the Latte software control the FPGA board(TSW14J58EVM) also?

When I open the Latte and HSDC together, USB connection lost.

It looks like the Latte could control the FPGA board but somehow FPGA is not correctly set up if I use Latte only.

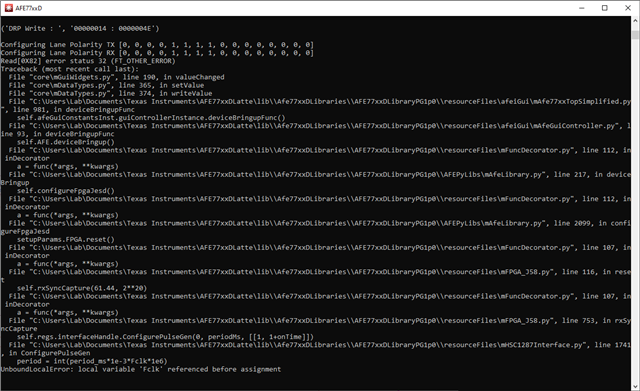

Does the JTAG and Vivado are essential?

I thought JTAG is optional, and I did not use the JTAG connection. Could it be related with the FPGA set up issue of Latte?

I want to start testing TX first.

I am checking the TX port with SA and change settings.

I only could see the LO leakage for short period of time, and it disappeared.

So it means, AFE7769D could be set correctly, I guess there is no Baseband signal and it stopped.

Document sbasag4a page 174 shows the device can work with Fref down to 122.88Mhz.

I thought the AFE7769D could accept 122.88Mhz as a ref CLK but the Latte software config tab does not allow me to set.

The pull-down menu of config tab only shows 245.76MHz, 368.64MHz, 491.52Mhz

I think the config tab should includes the 122.88MHz on the pull-down menu.

When I start HSDC, I saw "Firmware version and dll version does not match" message.

How could I solve the issue?

Thank you in advance for the help.