Other Parts Discussed in Thread: AFE7769, AFE7769EVM, TSW14J58EVM

Hi expert,

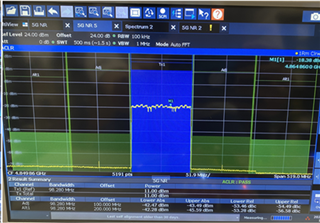

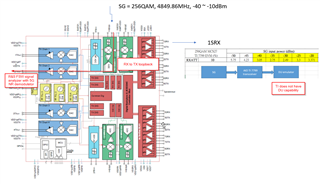

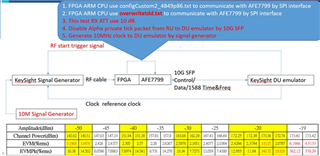

Customer measured Rx EVM of AFE7799 on their board and got over 2.5%. Would you please advise possible methods to improve Rx EVM?

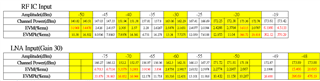

|

256QAM |

SG input power (dBm) |

||||||||

|

-50 |

-45 |

-40 |

-35 |

-30 |

-25 |

-20 |

|

||

|

RXATT |

10 |

5.75 |

4.23 |

3.05 |

2.75 |

2.49 |

3.3 |

3.371 |

|

Thanks,

Allan

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/220/UL-256QAM-EVM_5F00_AFE7799_5F00_RX_5F00_input.7z

https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/220/UL-256QAM-EVM_5F00_AFE7799_5F00_RX_5F00_input.7z