Other Parts Discussed in Thread: AFE7900EVM,

Hello,

We are testing AFE7900EVM board with Xilinx ZCU102 together,

using the design files that are included in 'ZCU102_AFE79xx_8b10b_10Gbps' folder in TI JESD204 IP reference designs.

We have tested TI-JESD204c-IP with TX/RX_LN_DATA_WIDTH = 64 mode successfully, now we want to change the data width to 32 bits

Followings are that we have changed

1. Change the LANE DATA WIDTH value in jesd_link_parms.vh

`undef RX_LANE_DATA_WIDTH

//`define RX_LANE_DATA_WIDTH 64

`define RX_LANE_DATA_WIDTH 32

`undef TX_LANE_DATA_WIDTH

//`define TX_LANE_DATA_WIDTH 64

`define TX_LANE_DATA_WIDTH 32

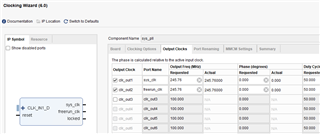

2. Change the output clock of sys_pll IP from 122.88MHz to 245.76MHz

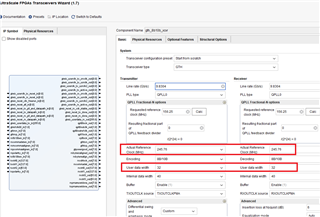

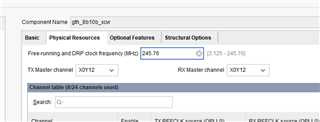

3. Change clock frequency and user data widh in transcevier ip

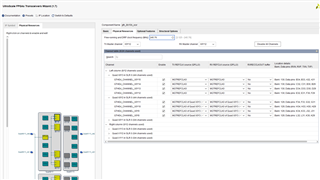

After then we tried to generate FPGA bitstrem , but it stopped with 'write_bitstream ERROR' like below picture shown.

Is there anything we missed to use 32-bit lane data width?

We are really appreciate any comments regarding this issue.

Thank you in advance.

-- Sangcheol