Tool/software:

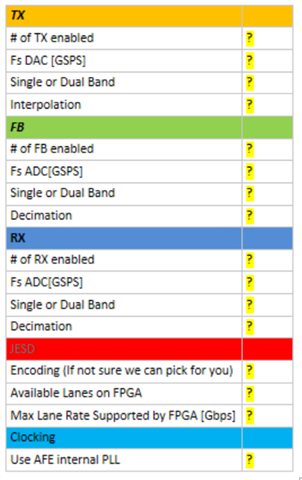

In our project, we plan to use the AFE7950 device, as follows:

- To use 4 ADC's and 4 DAC's;

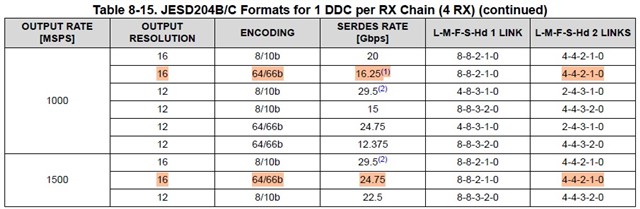

- 2 of the ADCs inputs signals are going to be configured with 1000 MSps output data sampling rate,

while the others 2 needs to be configured with 1500 MSps Output Rate;

- The same configuration is going to be used in the 4 DACs for the transmition flow;

- Our FPGA's transceivers are limited to 26 Gbps bit rates;

- Given these two requirements we have estimated the maximum number of bits per sample for both cases (1000MSps and 1500MSps)

as (26 bits(13I+13Q) and 16 bits(8I+8Q)):

13 bits x 2 (real(I) + imaginary(Q)) x 1GSps = 26 Gbps;

8 bits x 2 (real(I) + imaginary(Q)) x 1.5GSps = 24 Gbps;

- our ADCs must be configured with 1 DUC

Questions:

1. How can we configure the ADCs and DACs with this two numbers of bits (13x2(26b) and 8x2(16b))? Is the Latte software used for it ?

2. How the I and Q components of the data are going to be combined in a 64b66b format (for JESD204C) ?