Other Parts Discussed in Thread: AFE7900, AFE7950EVM, , AFE7950

Tool/software:

Hello everyone,

I am currently working on a project using the ZCU102 board in conjunction with the AFE7900. My goal is to directly write SPI commands from the FPGA to both the AFE7900 and LMK chips, bypassing the FTDI.

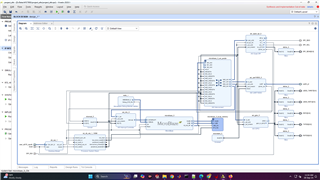

I have been following the instructions provided in the sbau412a document, and have successfully created a block design in Vivado. However, I'm facing some confusion when it comes to selecting the correct FPGA pin numbers for the output of the block diagram.

Specific Issues:

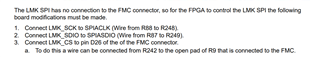

In Section 10 of the document, it discusses AFE79xxEVM Board Modifications. It mentions the SPI lines for the LMK’s chip select, which is associated with pin D26 of the FMC connector. The schematic refers to D26 as SPIASDO_FMC.

Should I use the D26 pin for the LMK’s chip select, or is this pin misidentified in the documentation? How should I correctly map the SPI lines (MOSI, MISO, SCLK, CS) for both the AFE7900 and LMK to FPGA pins?

Section 11 - AXI GPIO Configuration: The document also talks about configuring the AXI GPIO, but I am unclear on how to properly map these to the physical I/O pins of the FPGA for SPI communication.