Tool/software:

Hi,

We are use AFE7921 with some question.

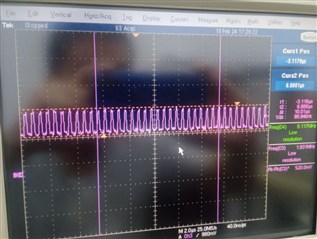

In the past, we used bandwidth with 200M,our AFE7921 config is below , and our sysref is 3.84MHz,JESD TX and JESD RX rate is 9.8304Gbps, it works stably.

sysParams.FRef = 245.76

sysParams.FadcRx = 2949.1

sysParams.Fdac = 2949.12*3

sysParams.ddcFactorRx = [12,12,12,12]

sysParams.ducFactorTx = [36,36,36,36]

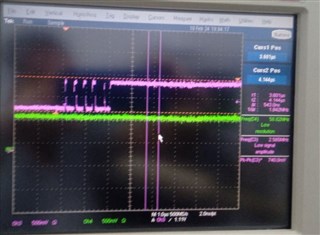

Now we used bandwidth with 100M to save FPGA resources and power, and sysref is 3.84MHz,,our AFE7921 config is below,the clk and ADC/DAC rate was the same,the DDC value is doubled .JESD TX and JESD RX rate is 4.9152Gbps But it works is not stably.,some times link down,and some times link up and then link down toggle.

sysParams.FRef = 245.76

sysParams.FadcRx = 2949.1

sysParams.Fdac = 2949.12*3

sysParams.ddcFactorRx = [24,24,24,24]

sysParams.ducFactorTx = [72,72,72,72]

We also try to change ADC/DAC rate,,our AFE7921 config is below. but the phenomenon is the same,it also works is not stably.,some times link down,and some times link up and then link down toggle.

sysParams.FRef = 245.76

sysParams.FadcRx = 1474.56

sysParams.Fdac = 1474.56*3

sysParams.ddcFactorRx = [12,12,12,12]

sysParams.ducFactorTx = [36,36,36,36]