Other Parts Discussed in Thread: AFE7950,

Tool/software:

Hello team!

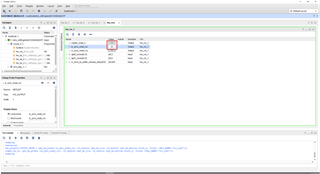

We have purchased AFE7950 evaluation board and configuring it with ZCU102 FPGA. For this we are using resources like .bit, .ltx & GUI from TI Secure Resources. Initially AFE was configured as in TI204c-Setup document. After programming qpll0 was getting locked as mentioned in document..

"In order to set up the FPGA to send Tx data out on the JESD lanes we first need to follow these steps:

- Take the master reset out of reset (Set master_reset_n to 1)

- When the master reset is 1 the qpllshould lock, indicated by a value of 3.

- Take the Tx sync out of reset (Set tx_sync_reset_vio to 0)"

But after some power cycles, when we try to configure it now, after programming FPGA, qpll0 is not getting locked i.e., qpll0_locked value is not changed. No code is modified in between. But even in multiple power cycles board is not configured properly.

Kindly help us resolve this issue!

Thank you