Tool/software:

Hi,

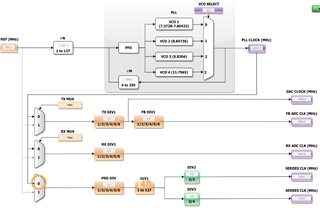

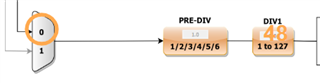

I have installed the AFE7950 device on a PCB co-located with a Xilinx FPGA which instantiates the TI_204c_IP_ref.sv design. I have previously instantiated the same design on the AFE7950EVM evaluation platform which sources a 491.52 MHz REFCLK. In our design, we are driving REFCLK at 500 MHz. We are directly sourcing this clock from a PLL because we eventually will directly source 12000 MHz as the sample clock to the DAC. Our method of bringup is:

1. configure the AFE7950EVM over SPI by running the attached scripts, setup_500.00_ddc48_fb24_duc96_DB.py in Latte

2. capture the SPI sequence from the Latte terminal

3. Perform all SPI writes and reads from the captured sequence on our custom PCB system

4. Capture 500.00_ddc48_fb24_duc96.log showing all SPI transactions in our custom PCB setup

I assume that the following sequence in the log is telling me that the PLL is not locked:Writing into 0x0066 value 0x00

Writing into 0x0066 value 0x01

Writing into 0x0066 value 0x03

Writing into 0x0063 value 0x41

Writing into 0x0063 value 0x01

Reading From 0x0066 value 0x03

Reading From 0x0066 value 0x03

Reading From 0x0066 value 0x03

Reading From 0x0066 value 0x03

Writing into 0x0066 value 0x31

I have taken some oscilloscope captures to investigate the behavior of REFCLK:

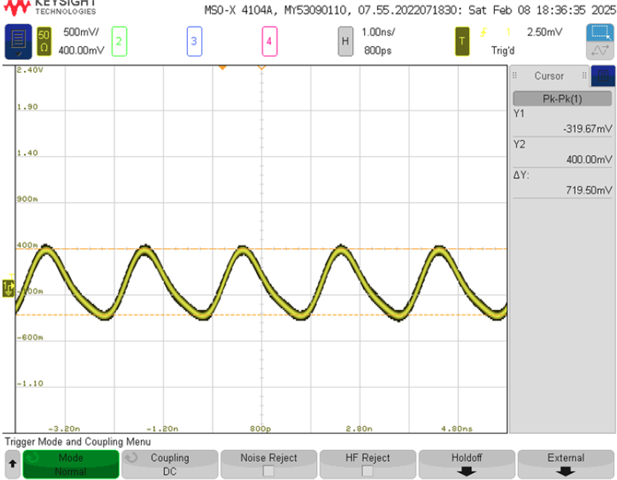

REFCLK+ with high impedance probe:

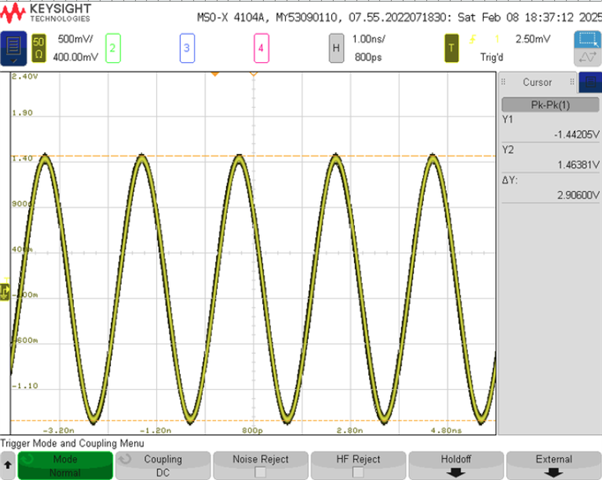

REFCLK- with high impedance probe:

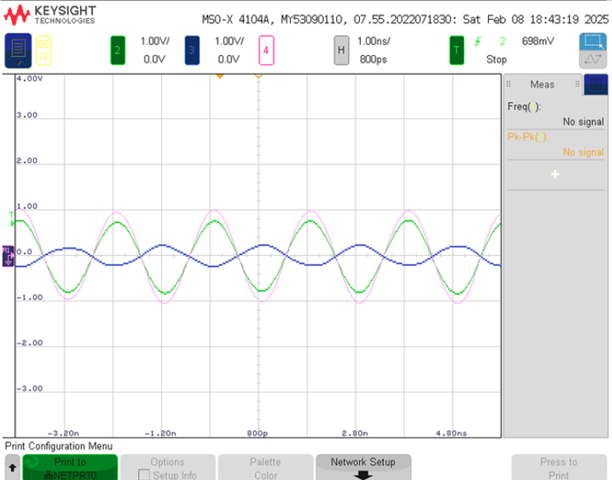

REFLK +/- and differential with low impedance probes:

I have measured the REFCLK frequency to be 500 MHz. I noticed an imbalance between the + and - legs. I also notice that the 2V swing (differential) exceeds the recommended operating condition of 1.8V Vppdiff by a small amount.

Do you think that reducing the amplitude of the differential swing is the correct course of action? Could you also take a look at my scripts and log and see if the scripts look correct and whether there is anything else in the log that indicates a different problem?

Thank you,

Jesse