Tool/software:

Hello

I had success bringing up the "TI ZCU102 8b10b" project, ZCU102_AFE79xx_8b10b_10Gbps, using the AFE7950EVM connected to the Xilinx ZCU102 development board. In this reference project there are 8 lanes

This project using the following settings:

- fpgaRefClk = 122.88

- FRef = 491.52

- FadcRx = 2949.12

- FadcFb = 2949.12

- Fdac = 2949.12*4

- LMFSHd = 44210

- K = 32

- LvdsSync = False

I follow the TI204c-Setup.docx:

- Power on ZCU102

- Power on AFE7950EVM

- Open Latte

- Run setup.py

- Run devInit.py

- Run ConfigLmk.py

- Program FPGA

- Release master_reset_n -> 1

- Release tx_reset -> 0

- Run ConfigAfe.py

- Release rx_reset -> 0

I modified some IP/file properly to be compliant to my goal, like GT and PLL, jesd_link_params.vh file and the constraints.xdc file. My goal are the following:

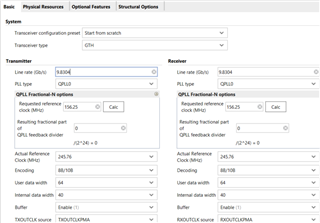

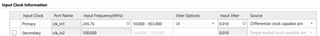

- fpgaRefClk = 245.76

- FRef = 245.76

- FadcRx = 2457.6

- FadcFb = 2457.6

- Fdac = 2457.6*4

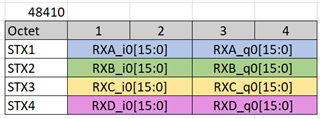

- LMFSHd = 24410

- K = 16

- LvdsSync = False

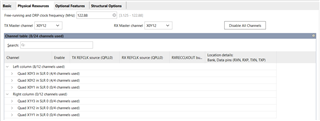

I change the GT config:

I change the PLL config:

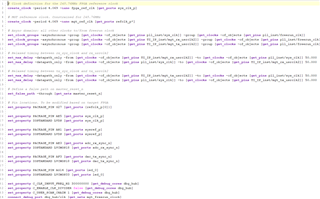

I change the jesd parameters in jesd_link_params.vh:

I change the constraints file:

I see the IQ mapping in the refdesign_tx.sv is the following:

For 64bit mapping LMFSHd = 24410 this IQ mapping must be change?

In which file can be found the IQ mapping table?