Part Number: LMX8410L

Tool/software:

Hi, I'll give you some context first:

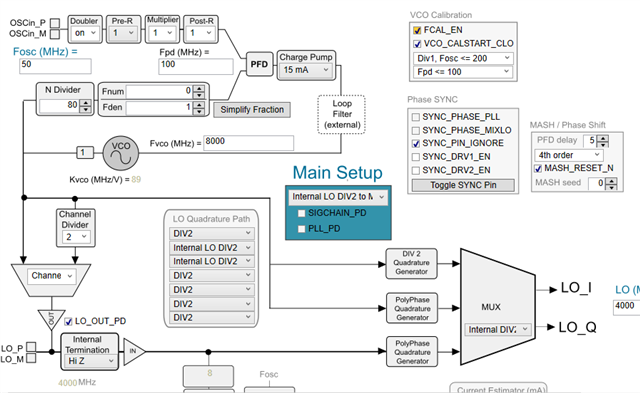

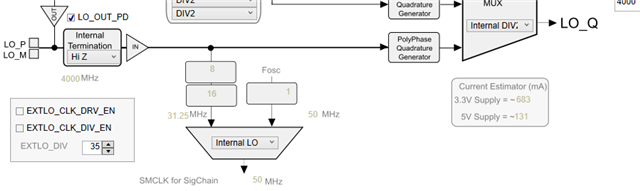

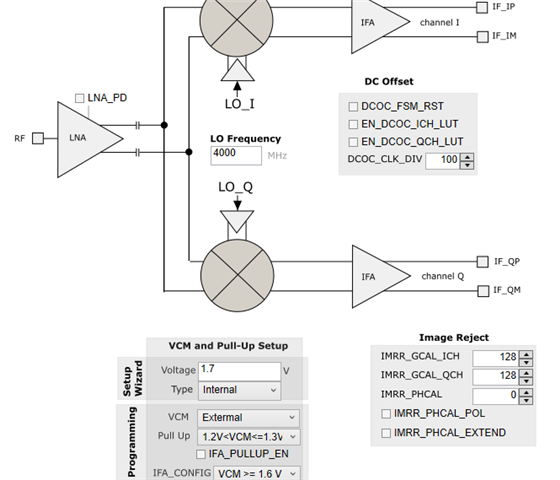

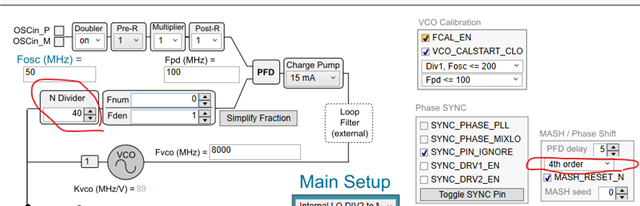

We are using this demodulator in a custom board because we want a LO of 7.2 GHz. We are using internal configuration with the VCO divided by CH_DIV.

The OSCIN is 50MHz and it comes through LVDS at 3.5mA with a DC Level of 1.6V per line. Then we use the doubler to take it to 100MHz.

For the Power Up Sequence we are manipulating the registers as It shows below: (I put only the registers that allow special configuration, the rest or them were obtained via TICS Pro and confirmed with the Datasheet as it recommends).

| REGISTER | DATA (hex) |

|---|---|

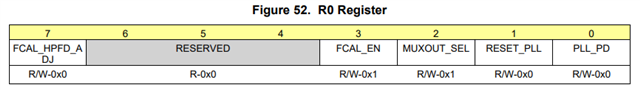

| 0 | 0x665C |

| 1 | 0x080B |

| 9 | 0x1604 |

| 10 | 0x1088 |

| 11 | 0x0018 |

| 14 | 0x13F0 |

| 36 | 0x0090 |

| 37 | 0x8204 |

| 38 | 0x0000 |

| 39 | 0x0001 |

| 40 | 0x0000 |

| 41 | 0x0000 |

| 42 | 0x0000 |

| 43 | 0x0000 |

| 44 | 0x1FA0 |

| 46 | 0x07FC |

| 75 | 0x0200 |

| 79 | 0x0000 |

| 80 | 0x0009 |

| 81 | 0x09D7 |

| 83 | 0x3221 |

| 84 | 0x1903 |

| 94 | 0x8080 |

| 95 | 0x0000 |

| 103 | 0x2C00 |

| 126 | 0x0000 |

We have checked the registers a lot of times, just to make sure we've are coding everything well, and it still getting hot (around 120°C). The Enable line comes from a PIC that we are programming with MPLAB and it communicates with the PLL via SPI, and the pin configuration is like in the Evaluation Board.

Do you know what else can we check? Any recommendation? Is it common to having temperature issues with this model? Please, if you read the code and found something, if you had experience with this chip, it would be really useful.